# UNIVERSIDAD TECNOLÓGICA DE LA MIXTECA

# Tarjeta de Adquisición de Datos con interfaz USB, empleando al Microcontrolador AT90USB646 de ATMEL

Tesis para obtener el título de:

Ingeniero en Electrónica

Presenta:

Magdiel Pascual García Juárez

Director de Tesis:

M.C. Felipe Santiago Espinosa

Huajuapan de León, Oaxaca; Mayo de 2013

| $\mathbf{r}$ | - 1 | •  |   | 4 |    |    |      |

|--------------|-----|----|---|---|----|----|------|

| I)           | ed  | 1  | വ | t | U  | rı | 2    |

|              | Cu  | 14 |   |   | ₹, |    | . Cu |

| $\sim$ | . 1      | c .     |   | • ~    |                  |

|--------|----------|---------|---|--------|------------------|

| Con    | especial | atecto  | v | carino | $\boldsymbol{n}$ |

| COIL   | cspeciai | cijecio | , | carno  | ci.              |

Mi madre

Juliana

Mis hermanos

Ignacio, Dolores, Griselda, Dolly y Francisco

Mi hija

Carolina

Mi esposa

Lorena

## Agradecimientos

A mi director de tesis el M.C. Felipe Santiago Espinosa por su amistad, el conocimiento y tiempo invertido en la realización de esta tesis.

A los profesores Fermín Hugo Ramírez Leyva, Heriberto I. Hernández Martínez, Hugo Suarez Onofre cuyas observaciones y sugerencias contribuyeron al mejoramiento de esta tesis.

A mi madre Juliana Juárez Meza porque gracias a sus consejos y palabras de aliento me fue posible concluir este trabajo de tesis.

A mi esposa Lorena Barragán por su apoyo y compresión durante todo el tiempo que duró el desarrollo del presente trabajo de tesis.

A mi padre José por su apoyo económico.

A la Universidad Tecnológica de la Mixteca por permitirme desarrollar el presente trabajo de tesis dentro de sus instalaciones.

# **Índice General**

| Dedicatoria | •••••                                  | iii          |

|-------------|----------------------------------------|--------------|

| Agradecimi  |                                        | v            |

| Índice Gene | eral                                   | vii          |

| ,           |                                        | xi           |

|             |                                        | xvii         |

| Resumen     |                                        | xix          |

|             |                                        |              |

| Capítulo 1  | Introducción                           | 1            |

| 1.1 Pla     | inteamiento del Problema               | 5            |

| 1.2 Jus     | stificación                            | 5            |

| 1.3 Ob      | jetivos                                | 6            |

| 1.3.1       |                                        | 6            |

| 1.3.2       | Objetivos particulares                 | 6            |

| 1.4 Or      |                                        | 7            |

| Capítulo 2  |                                        | 9            |

| 2.1 Mi      | crocontroladores                       | 9            |

| 2.1.1       |                                        | oladores9    |

| 2           | _                                      | cesamiento10 |

| 2           |                                        | 12           |

| _           |                                        |              |

|             |                                        |              |

|             | •                                      |              |

| _           | ,, , , , , , , , , , , , , , , , , , , |              |

|         | 2.1.1.6           | Puer     | to serie                                  | .12  |

|---------|-------------------|----------|-------------------------------------------|------|

|         | 2.1.1.7           | Entr     | adas/Salidas Digitales                    | .13  |

|         | 2.1.1.8           | Entr     | adas/Salidas Analógicas                   | .13  |

| 2.      | 1.2 Clasi         | ficacio  | ón de los Microcontroladores              | .13  |

| 2.      | 1.3 Orga          | nizaci   | ón de los Microcontroladores AVR de Atmel | .14  |

|         | 2.1.3.1           | El N     | úcleo AVR                                 | . 14 |

| 2.2     | Bus Univ          | ersal S  | erial                                     | .16  |

| 2.      | 2.1 Aspe          | ctos g   | enerales del USB                          | .16  |

| 2.      | 2.2 Histo         | oria y e | volución del USB                          | .16  |

| 2.      | 2.3 Área          | s de ap  | olicación                                 | .17  |

| 2.      | 2.4 Proto         | colo d   | le comunicación                           | .17  |

|         | 2.2.4.1           | Espe     | cificaciones Eléctricas                   | .21  |

|         | 2.2.4.2           | -        | cificaciones Mecánicas                    |      |

|         | 2.2.4.3           |          | cificaciones Funcionales                  |      |

|         | 2.2.4.4           |          | dos de los Dispositivos USB               |      |

|         | 2.2.4.5           |          | riptores USB                              |      |

| 2.3     |                   |          | rrollo LabVIEW                            |      |

|         |                   |          | las funciones de una biblioteca           |      |

|         |                   |          | un CIN                                    |      |

| 2.      | 3.3 Bibli         | oteca    | de Enlace Dinámico para un HID de Atmel   | .29  |

| Capítul | o 3               | Defin    | ición del sistema                         | 33   |

| 3.1     | Metodolo          | gía de   | desarrollo                                | .33  |

| 3.2     | Especifica        | ación (  | del producto                              | .35  |

| 3.3     | Definició         | n de H   | ardware y Software                        | .35  |

| 3.      | 3.1 Defin         | nición   | de Hardware                               | .36  |

|         | 3.3.1.1           | El M     | licrocontrolador AT90USB646               | .37  |

|         | 3.3.              | 1.1.1    | Controlador USB                           | . 39 |

|         | 3.3.              | 1.1.2    | Puertos de Entrada/Salida digitales       | . 41 |

|         | 3.3.              | 1.1.3    | Convertidor Analógico Digital             | . 42 |

|         | 3.3.              | 1.1.4    | Temporizadores                            | . 44 |

|         | 3.3.              | 1.1.5    | Modulación por Ancho de Pulso             |      |

|         | 3.3.              | 1.1.6    | Comunicación I2C                          |      |

|         | 3.3.              | 1.1.7    | Comunicación serial por SPI               | . 47 |

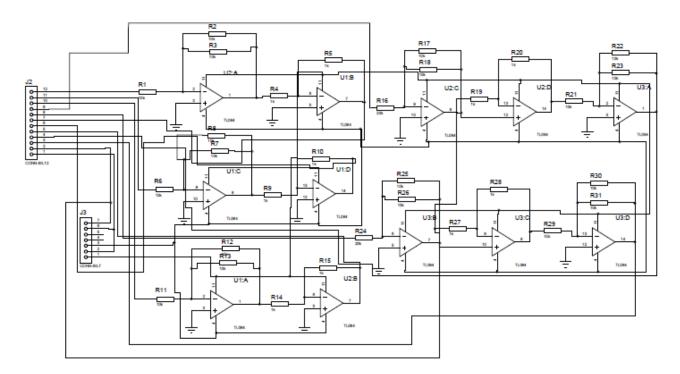

|         | 3.3.1.2           | Aco      | ndicionamiento de Señal                   |      |

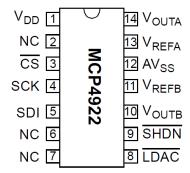

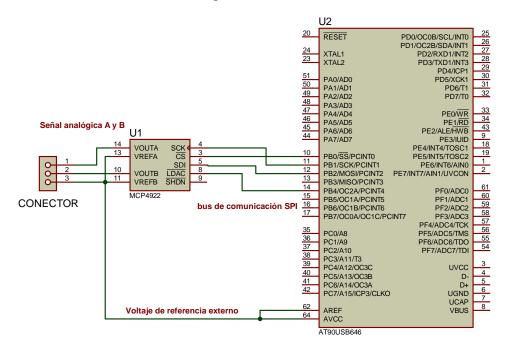

|         | 3.3.1.3           |          | vertido Digital-Analógico                 |      |

| 3.      |                   |          |                                           |      |

|         | 3.2 Defii         | nición   | del Software                              | JU.  |

|         | 3.2 Defir 3.3.2.1 |          | ware del Microcontrolador                 |      |

ix Índice de Figuras

|           | 3.3.2.2   | Interfaz Gráfica de Usuario                     | 51        |

|-----------|-----------|-------------------------------------------------|-----------|

| Capítulo  | 4         | Diseño del sistema                              | 53        |

| 4.1       | Diseño de | el Hardware                                     | 53        |

| 4.2       | Diseño de | el Software                                     | 56        |

| 4.2       | .1 Inter  | faz Gráfica de Usuario en la PC                 | 56        |

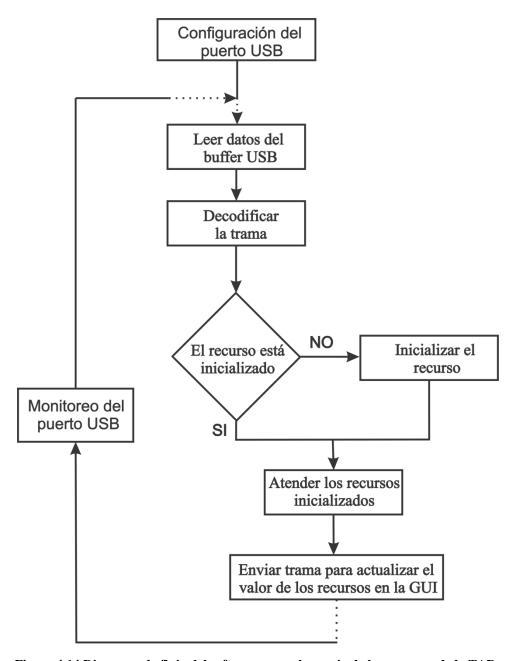

| 4.2       | .2 Softv  | ware del Microcontrolador                       | 64        |

| Capítulo  | 5         | Integración y pruebas                           | 69        |

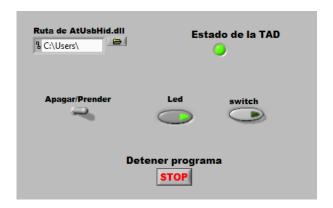

| 5.1       | Prueba co | omunicación micro-PC y viceversa                | 70        |

| 5.2       | Evaluacio | ón de los Módulos                               | 71        |

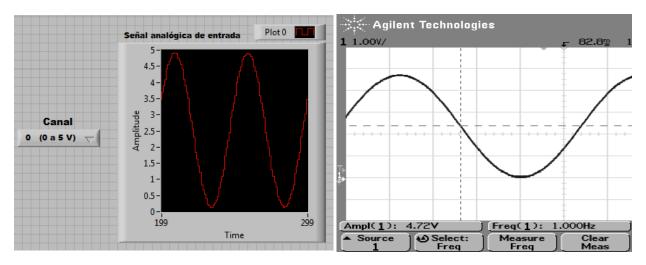

| 5.2       | .1 Prue   | ba del módulo ADC                               | 71        |

| 5.2       | .2 Prue   | ba del módulo PWM                               | 72        |

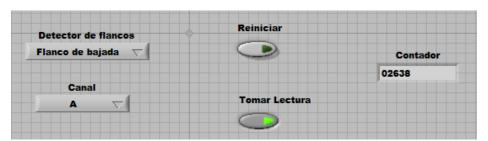

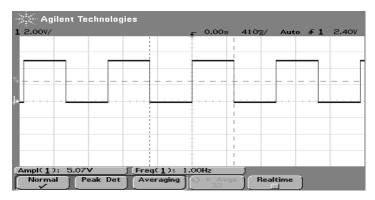

| 5.2       | .3 Prue   | ba del módulo Contador de Eventos               | 73        |

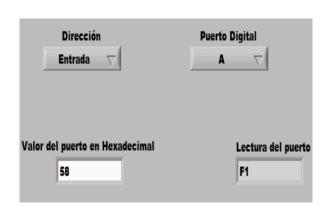

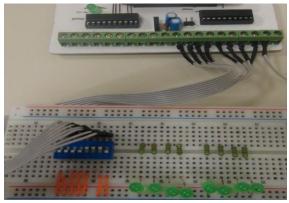

| 5.2       | .4 Prue   | ba del módulo Entradas/Salidas Digitales        | 74        |

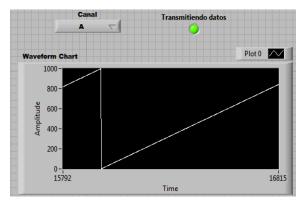

| 5.2       | .5 Prue   | ba del módulo Convertidor Digital Analógico     | 75        |

| 5.2       |           | ba del módulo I2C                               |           |

| 5.2       | .7 Med    | ición del tiempo de conversión del DAC y ADC    | 78        |

| 5.2       | .8 Prue   | ba de dos módulos en un mismo VI                | 79        |

| Capítulo  | 6         | Conclusiones y trabajos futuros                 | 81        |

| 6.1       | Trabajos  | futuros.                                        | 82        |

| Bibliogra | afía      | •••••                                           | 85        |

| Apéndic   | e A       | Tramas de configuración y monitoreo de los recu | ırsos A-1 |

| Apéndic   | e B       | Manual de Usuario                               | B-1       |

| Apéndic   | e C       | Circuitos y componentes empleados               |           |

# Índice de Figuras

| Figura 1.1 Diagrama de un sistema de adquisición de datos.                          | 2  |

|-------------------------------------------------------------------------------------|----|

| Figura 1.2 Ejemplos de Tarjetas de Adquisición de Datos [18,19].                    | 4  |

| Figura 2.1. Organización de un microcontrolador [21].                               | 10 |

| Figura 2.2. Elementos comunes en una CPU [21]                                       | 11 |

| Figura 2.3 Diagrama a bloques del núcleo AVR [10].                                  | 15 |

| Figura 2.4 Modelo de la capa de comunicación [7]                                    | 18 |

| Figura 2.5 Formato del paquete PID.                                                 | 19 |

| Figura 2.6 Formato del campo de dirección.                                          | 19 |

| Figura 2.7 Formato para el campo Endpoint.                                          | 19 |

| Figura 2.8 Cable USB [27].                                                          | 21 |

| Figura 2.9 Conectores USB [7]                                                       | 22 |

| Figura 2.10 Topología estándar USB [3]                                              | 23 |

| Figura 2.11 Estados de la unidad USB [7]                                            | 24 |

| Figura 2.12 Descriptor USB [3]                                                      | 26 |

| Figura 2.13 Módulo para llamadas a funciones de una biblioteca                      | 29 |

| Figura 2.14 Configuración de parámetros para las llamadas a funciones de biblioteca | 29 |

| Figura 2.15 Funciones DLL [25].                                                     | 30 |

| Figura 3.1 Diagrama de las fases para el diseño de un sistema embebido [2]          | 34 |

|-------------------------------------------------------------------------------------|----|

| Figura 3.2 Diagrama a bloques de la especificación del sistema.                     | 36 |

| Figura 3.3 Aspecto externo del microcontrolador AT90USB646 [10]                     | 38 |

| Figura 3.4 Diagrama a bloques del Controlador USB [10]                              | 40 |

| Figura 3.5 Alimentación del BUS para Unidades USB [10].                             | 41 |

| Figura 3.6 Esquemático para un pin de Entrada/Salida [10]                           | 42 |

| Figura 3.7 Pre-escalador del ADC [10].                                              | 43 |

| Figura 3.8 Hardware para el voltaje de referencia [10].                             | 43 |

| Figura 3.9 Definición del ciclo de trabajo                                          | 46 |

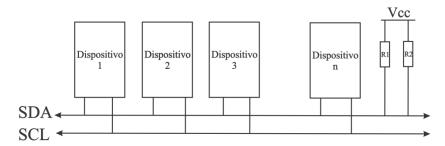

| Figura 3.10 Bus de interconexión TWI [10].                                          | 47 |

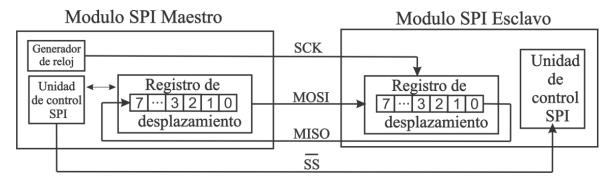

| Figura 3.11 Conexión entre 2 dispositivos vía SPI [21].                             | 48 |

| Figura 3.12 Circuito integrado MCP4922 [12].                                        | 50 |

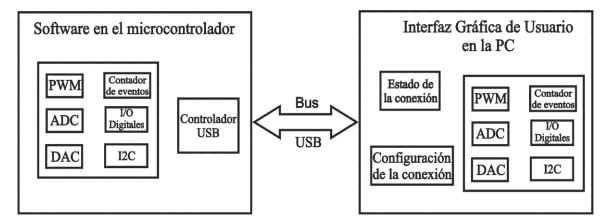

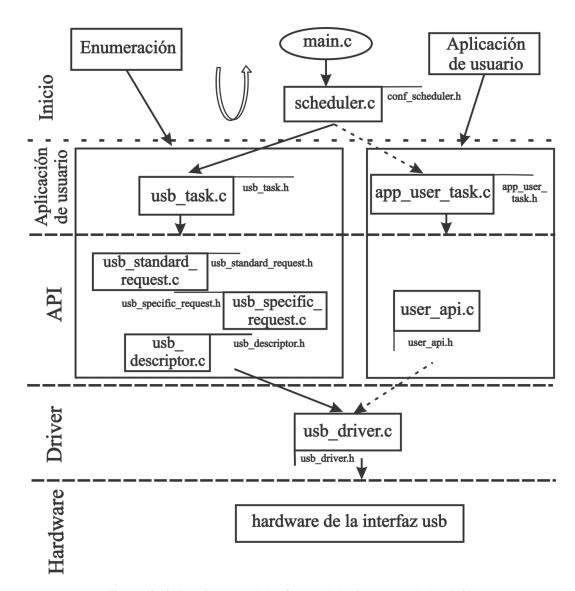

| Figura 3.13 Diagrama de la arquitectura del software.                               | 51 |

| Figura 4.1 Conexión de los puertos Digitales y salidas PWM                          | 54 |

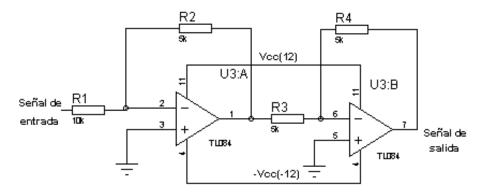

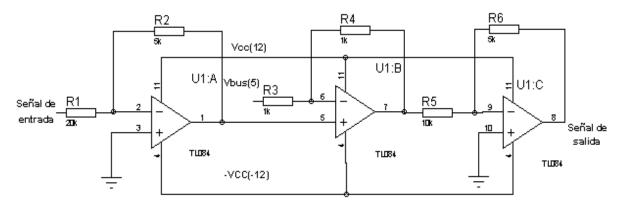

| Figura 4.2 Circuito acondicionador de señales para una entrada de 0 a 10V           | 55 |

| Figura 4.3 Circuito acondicionador de señales de entrada de -10 a 10V               | 55 |

| Figura 4.4 Diseño del Convertidor Analógico Digital.                                | 56 |

| Figura 4.5 Módulo para establecer la comunicación.                                  | 57 |

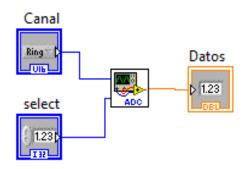

| Figura 4.6 Módulo para probar la comunicación.                                      | 58 |

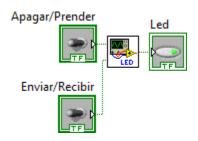

| Figura 4.7 Módulo para la configuración de E/S digitales.                           | 59 |

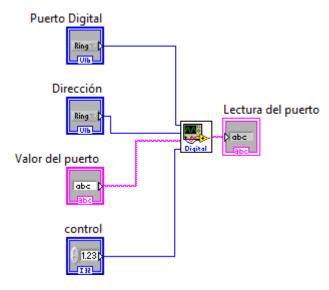

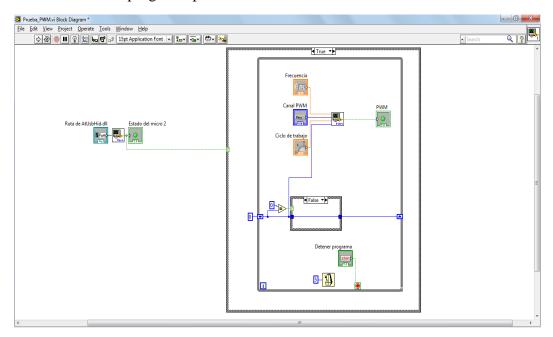

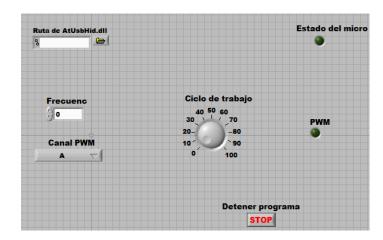

| Figura 4.8 Módulo para la configuración de las salidas PWM.                         | 60 |

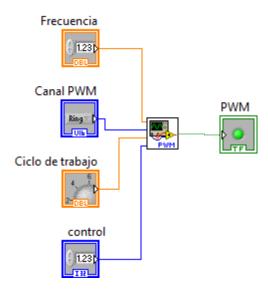

| Figura 4.9 Módulo para el manejo del ADC.                                           | 61 |

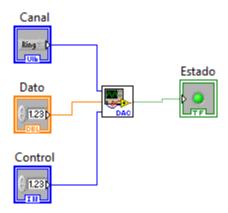

| Figura 4.10 Módulo para la configuración del DAC.                                   | 62 |

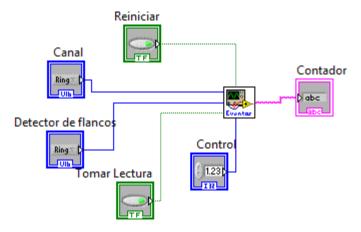

| Figura 4.11 Módulo para la configuración del contador de Eventos.                   | 63 |

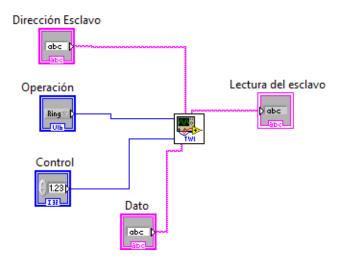

| Figura 4.12 Módulo para la configuración de la comunicación por I2C.                | 64 |

| Figura 4.13 Arquitectura del software del microcontrolador [19].                    | 65 |

| Figura 4.14 Diagrama de flujo del software para el manejo de los recursos de la TAD | 67 |

xiii Índice de Figuras

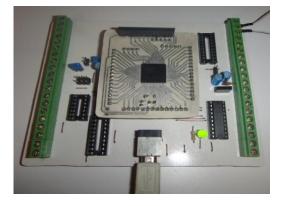

| Figura 5.1 Integración del Hardware y Software                                  | 69 |

|---------------------------------------------------------------------------------|----|

| Figura 5.2 Interfaz de usuario para la configuración de la conexión             | 70 |

| Figura 5.3 Interfaz del módulo para probar la comunicación.                     | 70 |

| Figura 5.4 Pruebas de la comunicación de la TAD con la PC                       | 70 |

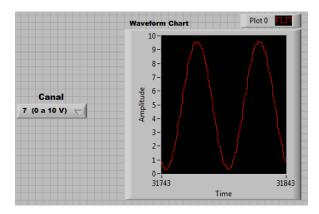

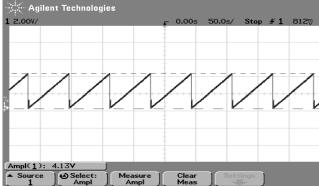

| Figura 5.5 Señal convertida de 0 a 5V.                                          | 71 |

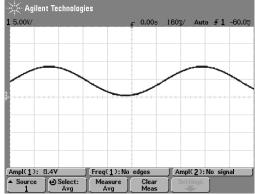

| Figura 5.6 Señal de entrada al ADC.                                             | 71 |

| Figura 5.7 Señal convertida de 0 a 10 V.                                        | 72 |

| Figura 5.8 Señal de entrada al ADC de 0 a 10 V                                  | 72 |

| Figura 5.9 Interfaz para la configuración de las salidas en PWM.                | 72 |

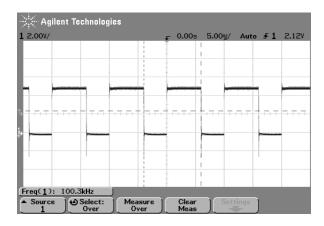

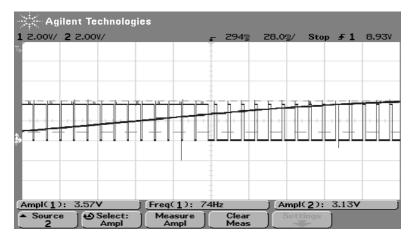

| Figura 5.10 Medición de la frecuencia del la señal PWM generada por la TAD      | 73 |

| Figura 5.11 Medición del ciclo de trabajo.                                      | 73 |

| Figura 5.12 Configuración del contador de eventos.                              | 73 |

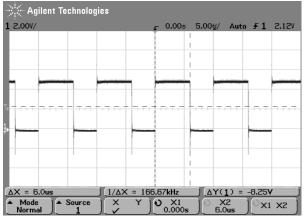

| Figura 5.13 Señal de prueba para el modulo contador de eventos.                 | 73 |

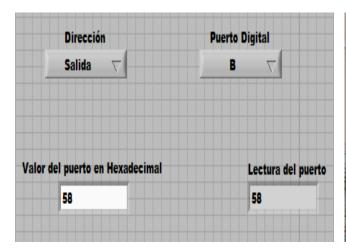

| Figura 5.14 Interfaz del módulo E/S digitales.                                  | 74 |

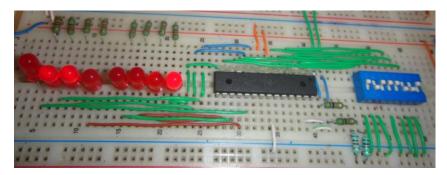

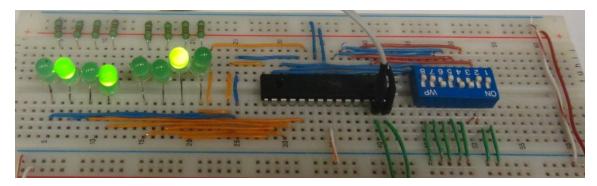

| Figura 5.15 Conexión física de las entradas al puerto B.                        | 74 |

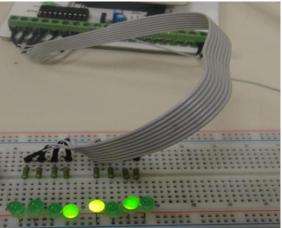

| Figura 5.16 Configuración del puerto digital B como salida                      | 75 |

| Figura 5.17 Salida del puerto digital B.                                        | 75 |

| Figura 5.18 Interfaz de configuración del módulo DAC y señal de prueba generada | 75 |

| Figura 5.19 Señal Convertida recuperada del osciloscopio.                       | 75 |

| Figura 5.20 Medición del tiempo de conversión.                                  | 76 |

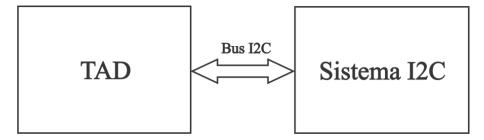

| Figura 5.21 Diagrama a bloques del sistema I2C.                                 | 76 |

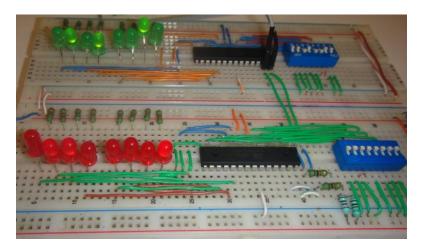

| Figura 5.22 Sistema de prueba para el módulo I2C.                               | 77 |

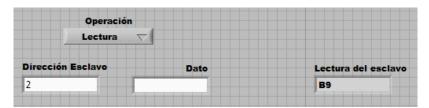

| Figura 5.23 Configuración de la GUI para la lectura del nodo Esclavo.           | 77 |

| Figura 5.24 Configuración del dato de entrada del nodo Esclavo 1.               | 77 |

| Figura 5.25 Configuración de la GUI para la escritura del nodo Esclavo 1        | 78 |

| Figura 5.26 Datos de salida del nodo Esclavo 2.                                 | 78 |

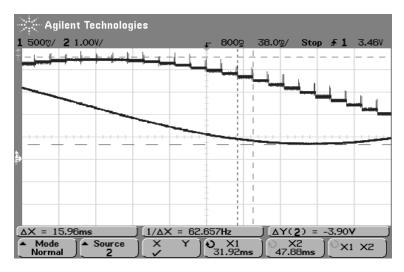

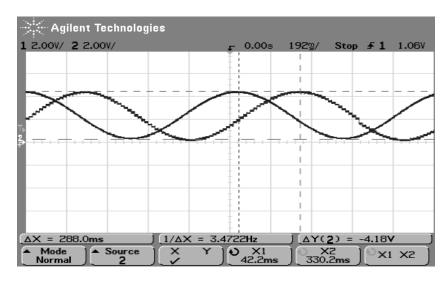

| Figura 5.27 Señal de entrada del ADC y señal de salida del DAC                  | 79 |

| Figura 5.28 Generación de una señal PWM a partir de una señal analógica | 79  |

|-------------------------------------------------------------------------|-----|

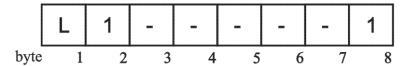

| Figura A.1 Trama Escribir-Led y Lectura-Led.                            | A-1 |

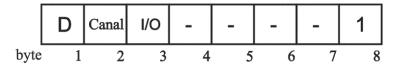

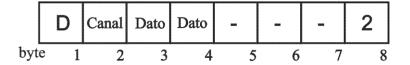

| Figura A.2 Trama Inicializar-Pdigital                                   | A-2 |

| Figura A.3 Trama Lectura-Pdigital                                       | A-2 |

| Figura A.4 Trama Escribir-Pdigital.                                     | A-2 |

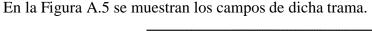

| Figura A.5 Trama Inicializa-PWM                                         | A-3 |

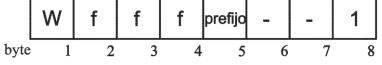

| Figura A.6 Trama Escritura-PWM                                          | A-3 |

| Figura A.7 Trama Inicializa-ADC.                                        | A-4 |

| Figura A.8 Trama Lectura-ADC.                                           | A-4 |

| Figura A.9 Trama Inicializa-DAC.                                        | A-4 |

| Figura A.10 Trama Escribir-DAC.                                         | A-5 |

| Figura A.11 Inicialización-Evento.                                      | A-5 |

| Figura A.12 Trama Escribe-Evento.                                       | A-5 |

| Figura A.13 Trama Lectura-Evento.                                       | A-6 |

| Figura A.14 Trama Inicializa_I2C.                                       | A-6 |

| Figura A.15 Trama Escritura_I2C.                                        | A-7 |

| Figura A.16 Trama Petición Lectura_I2C                                  | A-7 |

| Figura A.17 Trama de Lectura_I2C.                                       | A-7 |

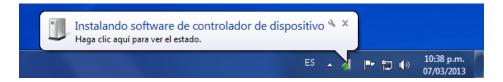

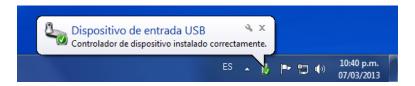

| Figura B.1 Mensajes de Windows mientras instala los drivers de la TAD   | B-1 |

| Figura B.2 Fin de la instalación del dispositivo.                       | B-1 |

| Figura B.3 Ventana del administrador de dispositivos.                   | B-2 |

| Figura B.4 Propiedades de la TAD.                                       | B-2 |

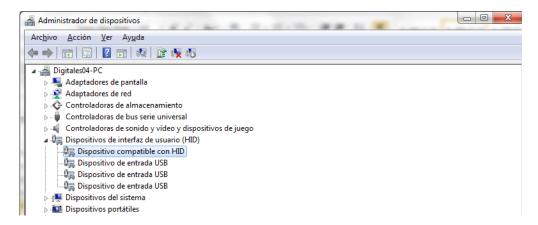

| Figura B.5 Paleta de funciones para buscar los módulos de los recursos  | B-3 |

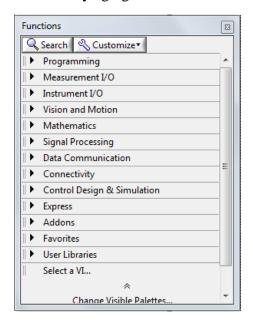

| Figura B.6 Ayuda del módulo PWM.                                        | B-3 |

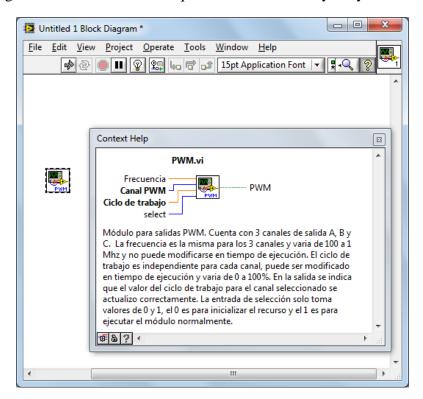

| Figura B.7 Código para el módulo PWM.                                   | B-4 |

| Figura B.8 Interfaz de usuario para el módulo PWM.                      | B-5 |

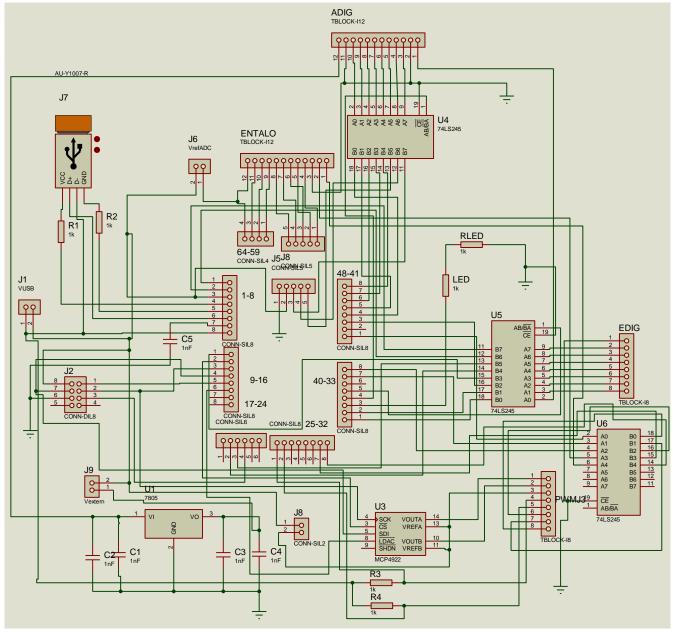

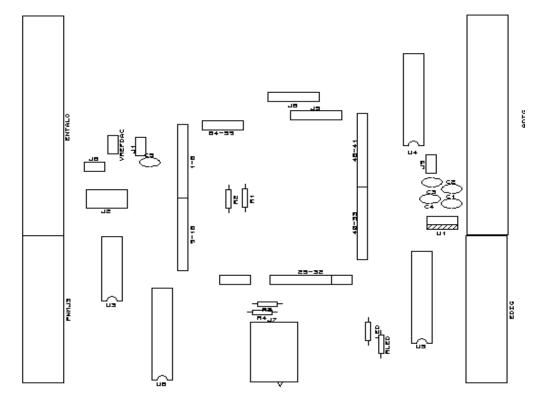

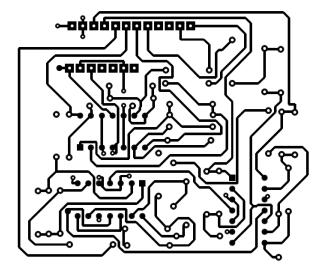

| Figura C.1 Diagrama esquemático de la placa base.                       | C-2 |

xv Índice de Figuras

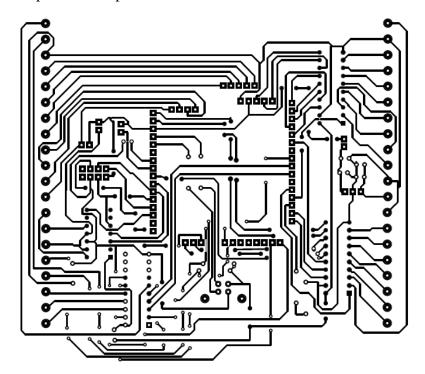

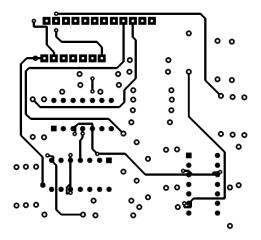

| Figura C.2 Diagrama de la placa base de la TAD.                          | C-5        |

|--------------------------------------------------------------------------|------------|

| Figura C.3 Montaje de los componentes de la placa base.                  | C-5        |

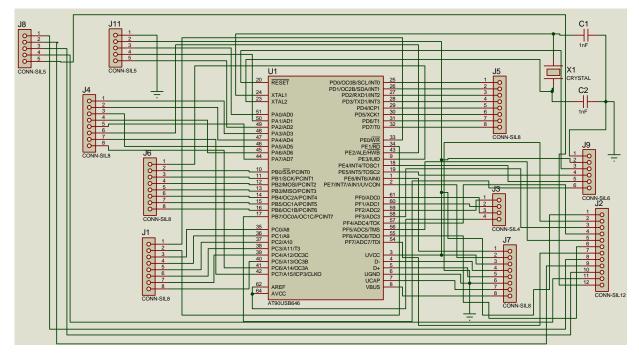

| Figura C.4 Diagrama esquemático para el microcontrolador.                | C-6        |

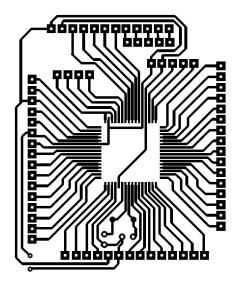

| Figura C. 5 PCB del microntrolador.                                      | C-7        |

| Figura C.6 Diagrama esquemático del circuito para el acondicionamiento d | le señales |

| analógicas                                                               | C-7        |

| Figura C.7 PCB del lado opuesto al de los componentes-                   | C-8        |

| Figura C.8 PCB del lado de los componentes.                              |            |

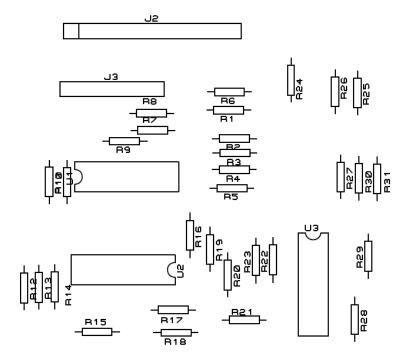

| Figura C.9 Diagrama de montaie de componentes.                           |            |

# Índice de Tablas

| Tabla 1.1Tabla de comparación en precio de las TAD                                | 5   |

|-----------------------------------------------------------------------------------|-----|

| Tabla 2.1 Versiones del USB                                                       | 17  |

| Tabla 2.2 Paquetes PID [7].                                                       | 20  |

| Tabla 3.1 Asignación de los puertos del microcontrolador a los recursos de la TAD | 39  |

| Tabla 3.2 Opciones para voltaje de referencia del ADC [10]                        | 44  |

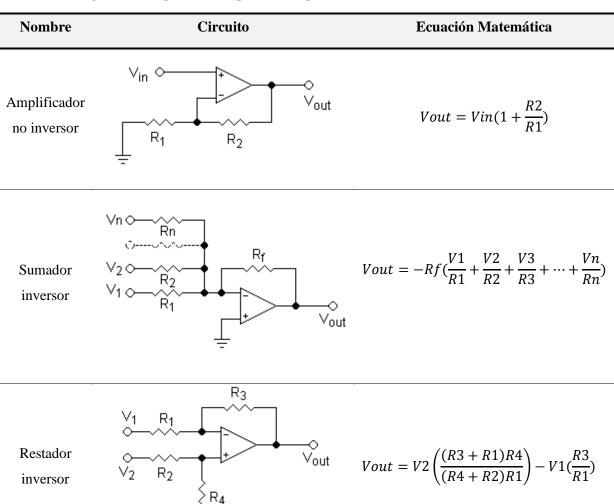

| Tabla 3.3 Configuraciones típicas del Amplificador Operacional                    | 49  |

| Tabla 4.1 Terminales del módulo para inicializar la comunicación.                 | 57  |

| Tabla 4.2 Terminales del módulo para probar la comunicación                       | 58  |

| Tabla 4.3 Terminales del módulo de E/S Digitales.                                 | 59  |

| Tabla 4.4 Terminales del módulo PWM                                               | 60  |

| Tabla 4.5 Terminales del módulo ADC.                                              | 61  |

| Tabla 4.6 Terminales del módulo DAC.                                              | 62  |

| Γabla 4.7 Descripción de las Entradas/Salidas del módulo de contador de Eventos   | 63  |

| Tabla 4.8 Descripción de las Entradas/Salidas del módulo de comunicación I2C      | 64  |

| Γabla C.1 Descripción de las terminales de entrada/salida.                        | C-3 |

| Tabla C. 2 Componentes de la placa base.                                          | C-4 |

| Tabla C. 3 Lista de componentes de la placa del microcontrolador.                 | C-6 |

| T-11-4- J- A J-11-12-12- J- 1 | D-4 : IICD              | 1111                        | - " A TOOT ICD ( AC )- | A TRACET |

|-------------------------------|-------------------------|-----------------------------|------------------------|----------|

| Tarjeta de Adquisición de l   | Datos con interiaz USB. | empleando al Microcontrolad | or A 1900 SB 040 de    | AIMEL    |

xviii

En el presente trabajo de tesis se muestra el diseño y construcción del hardware y software necesarios para la implementación de una Tarjeta de Adquisición de Datos con conexión USB a una computadora, bajo el sistema operativo Windows.

Se utilizó el microcontrolador AT90USB646 de ATMEL, ya que este cuenta con los recursos necesarios para implementar el protocolo de comunicación USB. Este microcontrolador es el encargado de controlar la inicialización y ejecución de los recursos así como la comunicación con la computadora.

El software que permite manejar los recursos de la tarjeta y la interfaz gráfica con el usuario se desarrolló en la plataforma de LabView. Se desarrolló un VI para cada recurso con los que cuenta la tarjeta, los cuales son:

- ADC con 8 canales de 10 bits.

- DAC con 2 canales de 12bits.

- Contador de Eventos.

- PWM con 3 canales.

- 2 puertos de E/S digitales de 8 bits.

- Puerto de comunicación I2C.

### Capítulo 1 Introducción

La instrumentación electrónica es el área de la tecnología que estudia los equipos realizados mediante circuitos y sistemas electrónicos, destinados a la medición, visualización, generación y conversión de señales eléctricas, así como los dispositivos o circuitos eléctricos que convierten una señal no eléctrica (temperatura, presión, etc.) en una señal eléctrica, que suelen recibir el nombre de sensores. De acuerdo con esto, los sistemas de instrumentación electrónica se pueden clasificar en tres grandes grupos [16]:

- a) *Instrumentos de medida y visualización*, son sistemas electrónicos que realizan la evaluación de uno o varios parámetros de una señal eléctrica y los presentan de forma gráfica, numérica o alfanumérica.

- b) *Instrumentos generadores de señal*, son sistemas electrónicos que tienen como misión generar señales eléctricas con características determinadas. Un ejemplo de este tipo de instrumento es el generador de señales.

- c) Instrumentos convertidores de señal, son dispositivos o circuitos electrónicos que convierten una señal eléctrica o no eléctrica, en otra señal eléctrica con características y rango determinados, sus parámetros contienen la información relevante de la primera señal.

En la actualidad existen diversos sistemas de instrumentación que combinan la instrumentación de medida, instrumentos generadores de señal e instrumentos convertidores de señal, por ejemplo un Sistema de Adquisición de Datos (SAD), puede ser definido como el conjunto de dispositivos lineales e interfaces que realizan la conexión entre los sensores de medición y una computadora, la cual realiza el procesado y almacenamiento de la información [15].

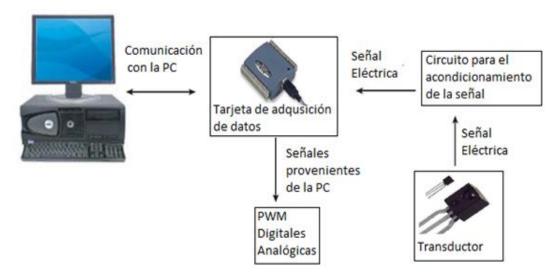

En la Figura 1.1 se muestra un diagrama a bloques de las partes que conforman un SAD.

Figura 1.1 Diagrama de un sistema de adquisición de datos.

El transductor permite tomar muestras de una señal física (temperatura, presión, intensidad luminosa, etc.) para convertirla en una señal eléctrica. Ciertos tipos de transductores requieren de un circuito adicional para ajustar los niveles de voltaje a los parámetros de entrada de la Tarjeta de Adquisición de Datos (TAD) y que ésta pueda interpretar los datos correctamente. Algunas TAD cuentan con este tipo de circuitos y el usuario debe tener en cuenta las características de la señal a introducir para evitar dañarla. La PC permite manipular o desplegar las señales digitales proporcionadas por la TAD, realiza algunas acciones de control y manda una respuesta a la TAD para que ésta genere señales de salida (analógicas o digitales) con ciertos parámetros de amplitud y frecuencia.

Una TAD es un dispositivo que digitaliza las señales eléctricas de manera que puedan ser procesadas y manipuladas a través de una interfaz de computadora. Los principales parámetros de una tarjeta de adquisición de datos son:

- El número de E/S analógicas,

- Número de E/S digitales,

- Contadores/temporizadores,

- Velocidad de muestreo,

- Puerto de comunicación,

- Precio.

La comunicación entre una TAD con una PC puede llevarse a cabo a través de diferentes puertos, como:

- Paralelo (LPT, Line Print Terminal),

- Puerto serial (RS-232, Recommended Standard),

- Componentes de conexión periférica (PCI, Peripheral Component Interconnect),

- Bus universal (USB, Universal Serial Bus),

- Ethernet.

En el mercado existe una gran variedad de modelos de TAD y su precio depende de las características con que cuente. En la Figura 1.2 se muestran dos ejemplos de TAD comerciales.

El gran avance en la tecnología ha propiciado que los sistemas electrónicos sean cada vez más compactos y fáciles de manipular por el usuario. Por su parte, las TAD han venido evolucionado y se han ajustado a las nuevas tecnologías, han podido migrar de conexiones internas de una PC, como el bus PCI, que si bien brinda una gran velocidad en la transmisión de datos, no es muy útil cuando se requiere que el sistema sea portable; posteriormente se popularizaron sistemas con conexiones a puertos externos como LPT y RS-232, los cuales dotaban al sistema de portabilidad.

- 8 entradas analógicas.

- 12 entradas/salidas digitales.

- 2 salidas analógicas.

- Bus de conexión USB 2.0 (12 Mb/s).

- Precio \$1,405 MN.

- Fabricada por National Instruments.

- Modelo NI-6008.

- 8 entradas analógicas.

- 16 entradas/salidas digitales,

- 2 salidas analógicas.

- Bus de conexión USB 2.0 (12 Mb/s).

- Precio \$130.00 USD.

- Fabricada por Measurement Computing

- Modelo PDM-1208FS.

Figura 1.2 Ejemplos de Tarjetas de Adquisición de Datos [18,19].

Actualmente en la mayoría de los sistemas electrónicos se ha estandarizado el puerto de comunicación USB, por su alta velocidad de transmisión de datos y su portabilidad. Por ello, las TAD que no trabajan en tiempo real, utilizan este puerto como medio de comunicación.

Por otro lado, el avance en el desarrollo de la arquitectura de los microcontroladores ha permitido incorporarle una mayor cantidad de recursos y mecanismos que permiten al usuario configurarlos con relativa facilidad.

Existe una gran gama de microcontroladores y cada uno cuenta con diferentes recursos que pueden ser usados para diversas aplicaciones.

Recientemente la compañía Atmel ha ampliado la familia AVR para incluir al microcontrolador AT90USB646, el cual cuenta contiene un módulo con la interfaz USB para realizar una comunicación con alguna PC. Esto lo hace factible para ser la base en el desarrollo de TAD.

Por ello, en esta tesis se desarrollará una TAD utilizando al microcontrolador AT90USB646, ya que los microcontroladores AVR son dispositivos de alto rendimiento ampliamente estudiados y usados en la UTM. Con esto se pretende profundizar en el conocimiento y evaluación de la familia AVR, permitiendo así comprender y manipular al

protocolo de comunicación USB y en un futuro inmediato poder desarrollar sistemas que utilicen esta interfaz en lugar de la interfaz serial estándar RS-232.

#### 1.1 Planteamiento del Problema

La interfaz de comunicación USB es ampliamente usada en una TAD porque permite que un sistema sea portable y de fácil conexión con la PC, brindándole mayor comodidad al usuario. Debido a esto, se plantea desarrollar una tarjeta de adquisición de datos basada en el microcontrolador AT90USB646, utilizando una comunicación vía USB y la clase para Dispositivos de Interfaz Humana (HID) proporcionada por Atmel Corporation.

La interfaz USB se vuelve muy compleja cuando los datos del usuario no se ajustan a las clases de la norma USB (almacenamiento masivo, audio, vídeo, etc.), deben desarrollarse controladores específicos, esto requiere una cantidad significativa de tiempo. Debido a esto, Atmel ha desarrollado una clase para Dispositivos de Interfaz Humana (HID), la cual asegura una transferencia dúplex completa entre el dispositivo y la PC, así ahorrar tiempo y esfuerzos de desarrollo [4].

Si además se cuenta con un ambiente de evaluación y desarrollo basado en LabView, se tendrá una herramienta eficiente para la implementación de diversas aplicaciones.

#### 1.2 Justificación

El desarrollo de una tarjeta de adquisición de datos representaría un costo de inversión bajo en comparación de las tarjetas más baratas que actualmente se encuentran en el mercado. La Tabla 1.1Tabla de comparación en precio de las TAD.Tabla 1.1 muestra un comparativo en precio de las tarjetas de adquisición de datos comerciales de menor costo, con un estimado para la tarjeta que se planea desarrollar en el presente trabajo.

Tabla 1.1Tabla de comparación en precio de las TAD.

| Fabricante de TAD       | Costo                        |

|-------------------------|------------------------------|

| National Instrument     | \$1,405MN                    |

| Measurent Computing     | \$139 dólares                |

| Tarjeta bajo desarrollo | \$700 MN (costos materiales) |

Una vez que se cuente con la TAD, podrá ser empleada en prácticas de laboratorio de diferentes cursos, como Metrología e Instrumentación, Sensores y Transductores, Control, etc. Y al ser esta de arquitectura abierta, los alumnos podrán agregar o quitar características para adecuarla a su aplicación.

Por otro lado, los estudiantes de las ingenierías de Electrónica y Mecatrónica de la UTM están familiarizados con los microcontroladores ATmega8 y ATmega16 de Atmel Corporation. El presente trabajo permitirá profundizar en el conocimiento y evaluación de la familia AVR y así poder migrar algunas aplicaciones al microcontrolador AT90USB646.

En consecuencia, las aplicaciones que actualmente se desarrollan utilizando la interfaz de comunicación RS-232, se podrán realizar con la interfaz de comunicación USB.

### 1.3 Objetivos

#### 1.3.1 Objetivo General

Desarrollar y construir una Tarjeta de Adquisición de Datos con interfaz USB, empleando el microcontrolador AT90USB646 de ATMEL.

#### 1.3.2 Objetivos particulares

- Evaluar la organización del microcontrolador AT90USB646 y comprender el funcionamiento de sus recursos internos orientados al manejo de la interfaz USB.

- Diseñar el hardware necesario para los recursos de la tarjeta.

- Desarrollar un programa para una PC bajo el entorno de desarrollo de LabVIEW para Windows.

- Evaluar la interacción de la tarjeta con la interfaz en la PC a través de la interfaz de comunicación USB.

- Documentar los resultados obtenidos, haciendo énfasis en el manejo de la interfaz USB del microcontrolador AT90USB646.

#### 1.4 Organización del documento

El documento comprende seis capítulos y tres apéndices, los cuales se describen a continuación.

Capítulo 1. Se muestra una introducción del documento, se plantean el problema, la justificación así como el objetivo general y los objetivos particulares.

Capítulo 2. Se da una descripción general sobre la arquitectura de los microcontroladores AVR y particularmente se describen los recursos del microcontrolador AT90USB646, seguidamente se exponen los aspectos generales del protocolo de comunicación USB y finalmente se describe la plataforma de desarrollo de LabVIEW.

Capítulo 3. Se explica la metodología de diseño empleada para el desarrollo de los módulos de entradas/salidas digitales y analógicas, I2C, contadores de eventos y PWM, para su implementación en el microcontrolador y en la interfaz gráfica de LabVIEW. Se detalla la organización del sistema.

Capítulo 4. Describe el diseño de los módulos con las herramientas de desarrollo, su estructura individual y posteriormente la integración del sistema.

Capítulo 5. Se muestra la interacción Software-Hardware. Se realizan las pruebas pertinentes para verificar la funcionalidad de los módulos.

Capítulo 6. Conclusiones obtenidas con los ejemplos de evaluación (adquisición y generación de señales digitales y analógicas, comunicación I2C, contador de eventos, prueba de PWM y verificación de comunicación). También se consideran posibles trabajos futuros.

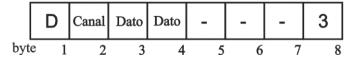

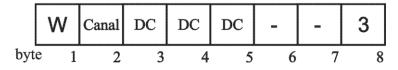

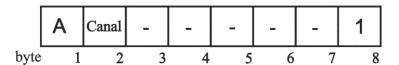

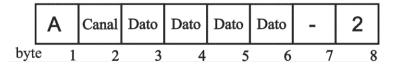

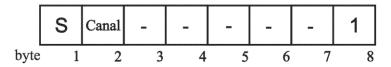

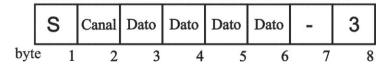

Apéndice A. Contiene la descripción de las tramas que se utilizan para la comunicación de la GUI con la TAD.

Apéndice B y C. Muestran los manuales de software y de hardware respectivamente. Brinda al usuario información de consideraciones técnicas necesarias para el uso de la TAD.

### Capítulo 2 Marco teórico

Este capítulo contiene una breve descripción de los conceptos fundamentales para la realización de una tarjeta de adquisición de datos, la cual se comunica con una PC a través del puerto USB Se describen las partes que conforman al sistema. La parte principal de una TAD es el microcontrolador que realiza las operaciones de adquisición y transferencia de datos, por eso es importante comprender su arquitectura. También se describe el protocolo de comunicación USB y el entorno de desarrollo de LabVIEW.

#### 2.1 Microcontroladores

Un microcontrolador es un Circuito Integrado con muy alta escala de integración (VLSI, *Very Long Scale Integration*), cuenta con más de 10,000 transistores. Internamente contiene una Unidad Central de Procesamiento (CPU, *Central Processing Unit*), memoria para código, memoria para datos, temporizadores, fuentes de interrupción y otros recursos necesarios para el desarrollo de aplicaciones, por lo general con un propósito específico [21].

### 2.1.1 Organización de los Microcontroladores

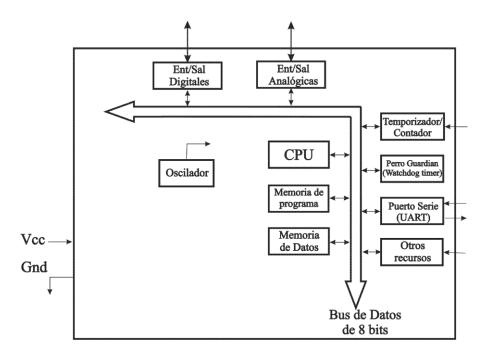

Existen diferentes fabricantes de microcontroladores y cada uno maneja diferentes familias con una variedad de modelos, sin embargo, hay bloques que son comunes a todos, en la Figura 2.1 se muestra la organización típica de un microcontrolador y en las siguientes secciones se describe cada uno de los bloques.

Figura 2.1. Organización de un microcontrolador [21].

#### 2.1.1.1 La Unidad Central de Procesamiento

La CPU administra todas las actividades del sistema y ejecuta todas las operaciones sobre los datos, mediante las instrucciones ubicadas en la memoria de código, con las cuales se determina el comportamiento del sistema.

El trabajo de la CPU puede resumirse en tres tareas fundamentales: captura de una instrucción, decodificación de la misma y ejecución. Las CPU pueden estar organizadas de diferentes maneras, de acuerdo con ello, pueden clasificarse como CISC o RISC. Con CISC se hace referencia a computadoras con un Repertorio de Instrucciones Complejo (CISC, *Complex Instruction Set Computer*) y RISC es para referir a computadoras con un Repertorio de Instrucciones Reducido (RISC, *Reduced Instruction Set Computers*) [21].

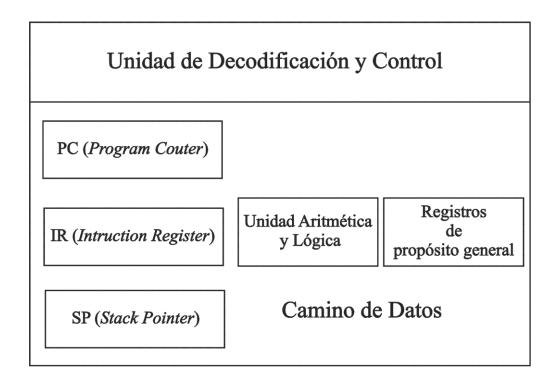

En la Figura 2.2 se muestran los bloques típicos de una CPU, los cuales se pueden clasificar en dos grupos; por una parte el *Camino de Datos y la Unidad de Decodificación* que involucra los elementos en los que puede fluir la información cuando se ejecuta una instrucción y por la otra tenemos el *Control*, el cual determina qué elementos se activan dentro del camino de datos para la correcta ejecución de una instrucción.

Figura 2.2. Elementos comunes en una CPU [21].

El Contador del Programa (PC, *Program Counter*), el Registro de Instrucción (IR, *Instruction Register*) y el Apuntador de Pila (SP, *Stack Pointer*), son registros con una función específica en una CPU.

El PC contiene la dirección de la instrucción que se va a ejecutar en un instante de tiempo determinado y mientras esa instrucción se ejecuta, el PC automáticamente actualiza su valor para apuntar a la siguiente instrucción a ejecutar. El registro IR contiene la cadena de bits que conforman la instrucción bajo ejecución, de esa cadena, la unidad de control considera el campo del opcode para determinar la activación de las señales en los demás elementos de la CPU. El SP contiene la dirección del tope de la pila, que es un espacio de almacenamiento utilizado durante la invocación de las rutinas. La Unidad Aritmética y Lógica (ALU, *Arithmetic Logic Unit*) es el bloque que se encarga de realizar las operaciones aritméticas y lógicas con los datos, también opera sobre direcciones para calcular el destino de un salto o la ubicación de una localidad a la que se tendrá acceso para una transferencia de memoria a registro o viceversa [21].

#### 2.1.1.2 Sistema de memoria

Una computadora (y por lo tanto, también un microcontrolador) debe contar con espacios de memoria para almacenar los programas (código) y los datos. En relación a cómo se organizan estos espacios, se tienen dos modelos de computadoras, un modelo en donde el código y datos comparten el mismo espacio de memoria (arquitectura Von Neumann) y el otro en donde se tienen memorias separadas, una para código y otra para datos (Arquitectura Harvard).

#### 2.1.1.3 Oscilador

La frecuencia a la que la CPU toma las instrucciones de la memoria del programa para su posterior ejecución, está determinada por el circuito de oscilación. El cual genera la frecuencia de trabajo a partir de un circuito RC, un resonador cerámico o un cristal de cuarzo externo.

#### 2.1.1.4 Temporizador/Contador

Es un registro de n bits que se incrementa con una señal de reloj interna o con eventos externos. En el primer caso funciona como temporizador y en el segundo como contador de eventos. Como temporizador es utilizado para manejar intervalos de tiempo y como contador es la base para programar alguna tarea cada que ocurra una cantidad predeterminada de eventos externos al microcontrolador.

#### 2.1.1.5 Perro Guardián

El Perro Guardián (WDT, *Watch Dog Timer*) es un temporizador que se compone de un registro de n-bits, cuando el WDT se desborda ocasiona un reinicio del sistema (*reset*). Su principal función es evitar que el microcontrolador se cicle en estados no contemplados.

#### 2.1.1.6 Puerto serie

La mayoría de los microcontroladores cuentan con un receptor/transmisor universal asíncrono (UART, *Universal Asynchronous Receiver Transceiver*), para comunicación serial

con dispositivos o sistemas externos, bajo protocolos y razones de transmisiones estándares. La comunicación serial puede ser de dos tipos:

- Síncrona: Además de la línea de datos se utiliza una línea de reloj.

- Asíncrona: Sólo hay líneas para los datos, el transmisor y el receptor se deben configurar con la misma velocidad de transferencia (bits/segundos, *Baud Rate*), además, se debe definir el mismo formato para cada trama.

#### 2.1.1.7 Entradas/Salidas Digitales

Los microcontroladores usan componentes de Entrada/Salida digitales para intercambiar datos con otros dispositivos. A diferencia de un puerto serie, en donde se transfiere un bit a la vez, en los puertos digitales es posible realizar un intercambio de bytes. Todos los microcontroladores cuentan con puertos digitales, aunque el número puede variar entre dispositivos.

#### 2.1.1.8 Entradas/Salidas Analógicas

Para entradas analógicas algunos microcontroladores incorporan Convertidores Analógico a Digital (ADC, *Analogic-Digital Converter*) o comparadores analógicos. Estos recursos permiten obtener información analógica del exterior, para monitorear parámetros como temperatura, velocidad, humedad, etc. Para salidas analógicas no es común que un microcontrolador incluya un Convertidor Digital a Analógico (DAC, *Digital-Analogic Converter*), para compensar esto, algunos microcontroladores incluyen salidas con Modulación por Ancho de Pulso (PWM, *Pulse Width Modulation*).

#### 2.1.2 Clasificación de los Microcontroladores

Existen diferentes formas de clasificar a los microcontroladores, a continuación se describen las clasificaciones típicas.

Por la arquitectura de la CPU, los microcontroladores pueden clasificarse como RISC o CISC, aunque casi todos los nuevos microcontroladores son RISC. Por el tamaño de los datos, se tienen microcontroladores de 4, 8, 16 y 32 bits, por el tamaño de los datos debe entenderse

el tamaño de los registros de trabajo y por lo tanto, corresponde con el número de bits de los operandos en la ALU. Tomando como base la organización y el acceso a la memoria de código y datos, se tienen 2 modelos: Arquitectura Von Neumann y Arquitectura Harvard. Considerando la forma en cómo se acceden a los datos para realizar las operaciones, se tienen cuatro modelos: Arquitectura tipo Pila, tipo Acumulador, tipo Registro a Memoria y tipo Registro-Registro [21].

#### 2.1.3 Organización de los Microcontroladores AVR de Atmel.

Los microcontroladores AVR incluyen un procesador **RISC** de **8 bits**, su arquitectura es del tipo **harvard** y sus operaciones se realizan bajo un esquema **Registro-Registro**. El núcleo AVR combina un conjunto de instrucciones con 32 registros de propósito general. Todos ellos están directamente conectados a la ALU, permitiendo que se tenga acceso a dos registros independientes en una sola instrucción ejecutada en un ciclo de reloj. La arquitectura resultante procesa al código de forma más eficiente, pues alcanza rendimientos hasta diez veces más rápido que los microcontroladores convencionales con arquitectura CISC [21,11].

#### 2.1.3.1 El Núcleo AVR

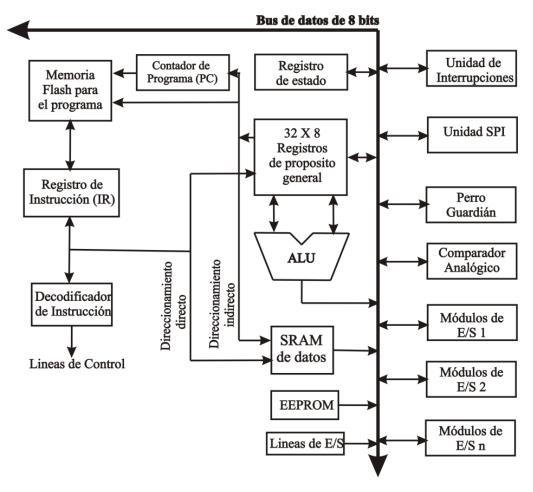

La organización interna de los microcontroladores de ATMEL se fundamenta en el núcleo AVR, el núcleo es la unidad central de procesamiento (CPU), es decir, es el hardware encargado de la captura, decodificación y ejecución de instrucciones, su organización se muestra en la Figura 2.3.

En torno al núcleo se encuentra un bus de 8 bits al cual están conectados los diferentes recursos del microcontrolador, estos recursos pueden diferir entre dispositivos. La principal función de la CPU es asegurar la correcta ejecución de programas. La CPU debe tener acceso a los datos, realizar cálculos, controlar periféricos y manejar interrupciones.

Para maximizar el rendimiento y paralelismo, el AVR usa una arquitectura Harvard con memorias y buses separados para el programa y para los datos. El programa se ubica en la memoria flash y los datos están en 3 espacios diferentes: En el archivo de registros (32 registros de 8 bits), en la SRAM y en la EEPROM [21].

Figura 2.3 Diagrama a bloques del núcleo AVR [10].

De la memoria flash se obtiene cada instrucción del programa y se coloca en el registro IR para su decodificación y ejecución. La memoria flash es direccionada por el registro PC o bien, por uno de los registros de propósito general. El PC es el registro que indica la ubicación de la instrucción a ejecutar, sin embargo, es posible que un registro de propósito general proporcione esta dirección a modo de que funcione como apuntador y se haga un acceso utilizando direccionamiento indirecto [21].

La ALU soporta operaciones aritméticas y lógicas entre los 32 registros de propósito general o entre un registro y una constante, para cualquier operación, al menos uno de los operandos es uno de los registros. Los 32 registros son la base para el procesamiento de datos porque la arquitectura es del tipo registro-registro, esto implica que si un dato de SRAM o de EEPROM va ser modificado, primeramente deberá ser llevado a cualquiera de los 32 registros de 8 bits, dado que todos tienen la misma jerarquía [21].

#### 2.2 Bus Universal Serial

En esta sección se describe el proceso evolutivo y las áreas de aplicación del protocolo de comunicación del Bus Universal Serial (USB, *Universal Serial Bus*), así mismo, se describe brevemente la especificación USB 2.0.

#### 2.2.1 Aspectos generales del USB

El USB es un estándar de comunicaciones industrial que define los cables, conectores y protocolos usados en un bus para el intercambio de datos entre una computadora y una amplia gama de periféricos. Permite conectar, comunicar y proveer de alimentación eléctrica, desde el mismo bus.

Los periféricos conectados comparten el ancho de banda USB a través de un protocolo basada en mensajes (*tokens*) [11]. El bus permite que los periféricos puedan ser conectados, configurados, utilizados y desconectados, mientras que el Host y otros periféricos se encuentran en operación [17].

En la actualidad, prácticamente todos los dispositivos portátiles utilizan la interfaz USB para conectarse con una PC. Como estos productos han aumentado su popularidad, hay una creciente necesidad de comunicación entre los dispositivos portátiles y una computadora vía USB y directamente entre dispositivos cuando una computadora no está disponible [17].

#### 2.2.2 Historia y evolución del USB

En 1995 las compañías *Intel, HP, Microsoft, Renesas Electronics y ST-Ericsson* crearon y estandarizaron el USB bajo el auspicio de una organización llamada Foro de Implementadores del Bus Universal Serial (USB-IF, *Universal Serial Bus Implementers Forum*). El objetivo fue crear un bus serial de baja y alta velocidad que permitiera el acceso compartido, disponibilidad, robustez, auto configuración y facilidad de uso [1].

Un hecho importante que permitió que sistemas con conexiones USB evolucionaran para ser más eficientes fue que las computadoras han alcanzado rendimientos cada vez mayores y son capaces de procesar grandes cantidades de datos. Además, nuevos tipos de dispositivos, formatos de medios de comunicación y de almacenamiento de bajo costo están convergiendo en brindar a los usuarios finales una mayor funcionalidad. En la Tabla 2.1 se muestran las diferentes versiones de la interfaz USB y sus principales características [23,27].

Tabla 2.1 Versiones del USB.

| Version<br>USB | Velocidad de<br>Transmisión                                    | Tipo de<br>Transmisión           | Año de<br>publicación |

|----------------|----------------------------------------------------------------|----------------------------------|-----------------------|

| USB 1.1        | Baja (1.5 Mbps)<br>Completa (12Mbps)                           | Half duplex                      | 1996                  |

| USB 2.0        | Baja (1.5Mbps)<br>Completa (12Mbps)<br>Alta (480Mbps)          | Flujo de datos<br>unidireccional | 2000                  |

| USB 3.0        | Baja (1.5Mbps) Completa (12Mbps) Alta (480Mbps) Súper (5 Gbps) | Dual-simplex                     | 2009                  |

# 2.2.3 Áreas de aplicación

El USB se ha convertido en una interfaz de comunicación muy popular, debido a su simplicidad para las aplicaciones de usuario final (*Plug and Play*, sin necesidad de reiniciar).

Puesto que el USB es un estándar para la conexión de periféricos, dispositivos como ratones, teclados, joysticks, escáneres, cámaras digitales, teléfonos móviles, reproductores multimedia, impresoras, sistemas de adquisición de datos, módems, tarjetas de red, tarjetas de sonido, discos duros externos, gadgets y demás dispositivos de interfaz humana usan este bus para comunicarse con la PC [7].

#### 2.2.4 Protocolo de comunicación

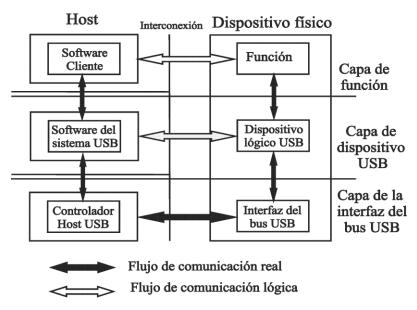

Como se muestra en la Figura 2.4, la conexión de un dispositivo USB con el Host requiere la interacción entre un número de capas y entidades. La capa de la interfaz del bus USB proporciona una conexión física, señalización de la conexión y conectividad de los paquetes entre el Host y un dispositivo USB. En esta capa se encuentra el controlador host USB, el cual integra hardware y software que permite a los dispositivos USB ser conectados a un host [7].

En la capa de dispositivo USB, el software del sistema USB (software que soporta el estándar USB en un sistema operativo en particular) utiliza el controlador Host para gestionar las transferencias de datos entre el host y los dispositivos USB.

Figura 2.4 Modelo de la capa de comunicación [7].

Los dispositivos USB que proveen de funcionalidad adicional al Host son conocidos como funciones. El cliente describe todas las entidades de software que son responsables de la interacción directa con los dispositivos USB. Cuando los dispositivos están conectados al sistema, estos clientes pueden interactuar directamente con el hardware periférico [7].

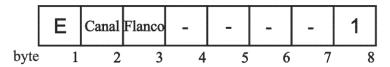

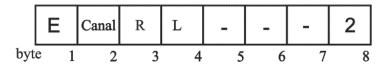

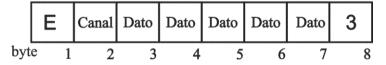

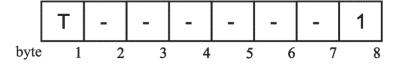

El protocolo de acceso al canal de comunicación (*media access protocol*) es de tipo *polled* (con sondeos continuos sobre la configuración). En el USB, lo datos se envían de manera serial, agrupados en paquetes. Los paquetes se agrupan para formar las Transacciones y las Transacciones se agrupan para formar las Transferencias. Las Transferencias son las estructuras de datos que tienen sentido para el Software que se ejecuta en el Host (Maestro en un sistema USB) [7].

Cada transacción se inicia cuando el controlador Host envía un paquete denominado token, describiendo el tipo y la dirección de la transacción, la dirección del dispositivo USB y el número del finalizador (endpoint). El dispositivo USB que es direccionado se encarga de decodificar apropiadamente el campo de dirección. En una determinada transacción, los datos se transfieren ya sea desde el host a un dispositivo o desde un dispositivo a la máquina. La fuente de la transacción posteriormente envía un paquete de datos o indica que no tiene datos que enviar. El destinatario, por lo general, responde con un paquete llamado handshake para que ambas partes se reconozcan [7].

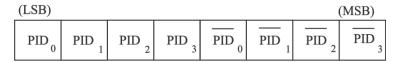

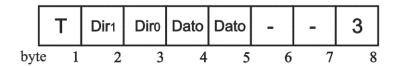

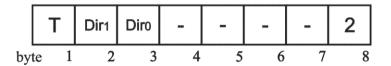

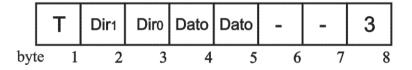

Todos los paquetes comienzan con un campo de sincronización (SYNC), utilizado por el hardware de entrada para alinear los datos entrantes con el reloj local. Un identificador de paquete (PID, *Identifier Packet*) sigue inmediatamente después del campo de sincronización en cada paquete de USB. Consta de un campo de cuatro bits para el tipo de paquete seguido por un campo de cuatro bits de verificación como se muestra en la Figura 2.5 [7].

Figura 2.5 Formato del paquete PID.

El PID indica el tipo de paquete y, por inferencia, el formato del paquete y el tipo de detección de errores aplicados al paquete. Un error del PID existe si los cuatro bits de verificación PID no se complementan de sus respectivos bits de paquetes de identificación. En la Tabla 2.2 se muestra los tipos de paquetes PID y una breve descripción [7].

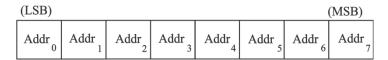

Seguido del campo PID está el campo de dirección (*ADDR*) para indicar el destino del paquete. Consta de 7 bits, por lo que permite que puedan ser direccionados hasta 127 dispositivos. En la Figura 2.6 se muestra el formato del campo de dirección [7].

Figura 2.6 Formato del campo de dirección.

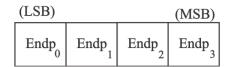

En seguida está el campo del *Endpoint* (ENDP) que consta de 4 bits, en la Figura 2.7 se muestra el formato de este campo. Permite mayor flexibilidad direccionando a las funciones en las que se requiere más de un *Endpoint*. Excepto por el *Endpoint* cero, los números del *Endpoint* corresponden a funciones específicas [7].

Figura 2.7 Formato para el campo Endpoint.

Posteriormente se encuentra el campo de número de muestras (*Frame number field*) compuesto por 11 bits y es incrementado por el Host en cada muestra. A continuación está el campo de datos, el cual varía entre 0 y 1024 bytes. Después del campo de datos se encuentra el

verificador de redundancia cíclica (CRC, *Cyclic Redundancy Checks*) considerado como campo de protección [7].

Tabla 2.2 Paquetes PID [7].

| Tipo de paquete<br>PID | Nombre     | Descripción                                                                                                             |  |

|------------------------|------------|-------------------------------------------------------------------------------------------------------------------------|--|

|                        | OUT        | Informa al dispositivo que el Host va a enviar información                                                              |  |

| Token                  | IN         | Informa al dispositivo que el Host va a leer información                                                                |  |

| Токеп                  | SOF        | Marcador de inicio de trama y número de muestras (frame)                                                                |  |

|                        | SETUP      | Se usa para comenzar el control de transferencia                                                                        |  |

|                        | DATA 0 y 1 | Paquete de datos par e impar                                                                                            |  |

| Data                   | DATA2      | Paquete de datos PID de alta velocidad, gran acho de banda para transacciones isócronas de micro-muestras (microframes) |  |

|                        | MDATA      | Paquete de datos PID de alta velocidad para la división y gran ancho de banda de transacciones isócronas.               |  |

|                        | ACK        | Permite saber que el paquete se recibió con éxito                                                                       |  |

| Handshake              | NAK        | El Receptor no puede aceptar los datos o el Transmisor<br>no puede enviar datos                                         |  |

| Hanasnake              | STALL      | El <i>Endpoint</i> está detenido o una solicitud en un segmento de control está detenida.                               |  |

|                        | NYET       | No hay respuesta del receptor                                                                                           |  |

|                        | PRE        | ( <i>Token</i> ) Habilita el tráfico del bus a dispositivos de baja velocidad                                           |  |

|                        | ERR        | (Handshake) Error de transacción                                                                                        |  |

| Special                | SPLIT      | Provee transacciones adicionales                                                                                        |  |

|                        | PING       | ( <i>Token</i> ) Sondeo del control de flujo de alta velocidad para un <i>Endpoint</i> tipo <i>bulk</i> /control        |  |

|                        | Reserved   | Reservado                                                                                                               |  |

## 2.2.4.1 Especificaciones Eléctricas

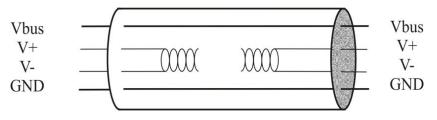

Los datos son transmitidos en forma serie, a través de 2 líneas denominadas V+ y V-. Además, la interfaz USB cuenta con 2 líneas para establecer los niveles de voltaje (VCC y GND), toman la alimentación del Host o de una fuente externa (5 V, 500 mA máximo). En la Figura 2.8 se muestra la organización del cable USB [7].

Figura 2.8 Cable USB [27].

La comunicación en un sistema USB se hace punto a punto a tres diferentes velocidades [7, 6].

- Baja velocidad (*Low-Speed*) es de 1.5 Mb/s.

- Máxima velocidad (Full-Speed) es de 12 Mb/s.

- Alta velocidad (*High-Speed*) es de 480 Mb/s

El nivel de voltaje que define a cada estado varía dependiendo de la velocidad que se esté empleando. Para baja velocidad, se toma un 1 diferencial cuando D+ es menor a 2.8V y D- no es mayor que 0.3V respecto a la señal de tierra. Se toma como un 0 diferencial cuando D- es menor a 2.8V y D+ no es mayor que 0.3V con respecto a tierra.

Para velocidad completa, se toma un 1 diferencial cuando D+ es menor a 2 V respecto a tierra y la diferencia entre D+ y D- es mayor a 200mV. Se toma como 0 diferencial cuando D- es menor a 2V y la diferencia entre D+ y D- es mayor a 200 mV.

Para alta velocidad, se toma un 1 diferencial cuando D+ es menor a 0.36V y D- no es mayor a 0.01V. Un 0 diferencial existe cuando D- es menor que 0.36V y D+ no es mayor que 0.01V [7].

## 2.2.4.2 Especificaciones Mecánicas

Los dispositivos USB que operan en alta velocidad (480 Mbps) y velocidad completa (12 Mbps) requieren el uso de un cable blindado con dos conductores de potencia y conductores de par trenzados de señal. Para baja velocidad (1.5 Mbps) se recomienda, pero no

es necesario, el uso de un cable con conductores de par trenzado de señal. El icono USB en los conectores es un indicador visual para obtener la orientación correcta [7].

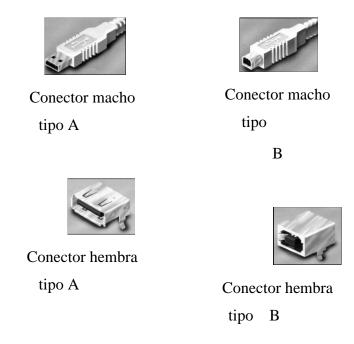

En la Figura 2.9 se muestran los tipos de conectores USB. Los conectores tipo A son el principal medio de conexión entre los dispositivos USB y un Host o el puerto de un hub o un dispositivo USB. Todos los dispositivos USB tienen el conector estándar macho tipo A. Los conectores tipo B permiten que los dispositivos USB cuenten con un cable estándar desmontable y el usuario final pueda reemplazarlo fácilmente [7].

Figura 2.9 Conectores USB [7].

## 2.2.4.3 Especificaciones Funcionales

Hay sólo un nodo Maestro (Host) en cualquier sistema con interfaz USB y éste es el operador maestro del bus, su interfaz USB puede ser implementada a partir de una combinación de hardware, firmware o software. El Host USB interactúa con los dispositivos USB a través del controlador Host [3].

Existen dos tipos de clases de dispositivos USB: hubs y unidades. Sólo los hubs tienen la capacidad de proveer puntos adicionales para conexión.

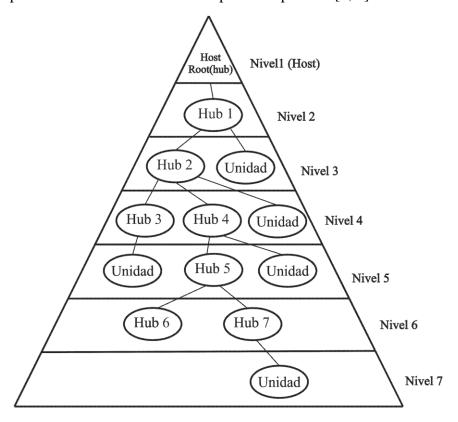

La topología física del bus USB es de tipo estrella. Cada segmento de cable es una conexión punto a punto entre el Host USB y un hub o un dispositivo USB. En la Figura 2.10

se muestra la topología de la interfaz USB. Debido a las limitaciones de tiempo de propagación en el hub y el cable, el número máximo de niveles es 7 (incluyendo el nivel del Host). El Host direcciona a los dispositivos Esclavos USB mediante un número de 7 bits, en consecuencia, es posible direccionar hasta 128 dispositivos por hub [7, 3].

Figura 2.10 Topología estándar USB [3].

Algunos ejemplos de dispositivos USB son:

- Dispositivos de interfaz humana, tales como ratones, teclados, controles de juegos, etc.

- Dispositivos de imagen como cámaras, escáner e impresoras.

- Dispositivos de almacenamiento masivo como drivers de CD-ROM, floppy y DVD.

## 2.2.4.4 Estados de los Dispositivos USB

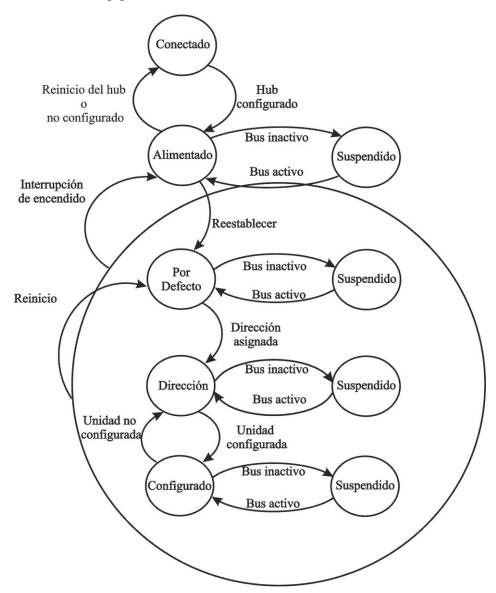

En la Figura 2.11 se muestran los estados de una unidad USB. Algunos son visibles para el Host USB y otros son internos de la unidad USB [7].

Cuando una unidad USB es conectada o desconectada del USB, el Host ejecuta un proceso llamado enumeración para identificar y manejar los estados de la unidad. Durante este

proceso, el servidor pregunta a la unidad algunos valores para identificar y cargar los controladores correctamente [7].

Figura 2.11 Estados de la unidad USB [7].

Cuando la unidad es conectada, se realizan las siguientes acciones [7]:

- El hub al que se conecta el dispositivo USB informa al Host del evento. En este punto, el dispositivo está en el estado de encendido y el puerto al cual se conectó está deshabilitado.

- El Host determina el motivo del cambio mediante la consulta al hub.

- El Host sabe a qué puerto se ha conectado el dispositivo USB, espera entonces por lo menos 100 ms para permitir la terminación del proceso de inserción y que se estabilice la conexión eléctrica. El Host emite un comando para activar y restaurar el puerto.

- Cuando la señal de reset (reinicio) se ejecuta, el puerto es habilitado. La unidad USB

está en el estado de Default (por defecto) y no puede utilizar más de 100mA del bus,

todos sus registros se han reiniciado y la unidad USB responde a la dirección por

defecto (cero).

- El Host asigna una dirección única a la unidad USB, cambiando a la unidad USB al estado dirección.

- Antes de que la unidad USB reciba una dirección única, el Host lee los descriptores de la unidad USB para determinar cuál es el tamaño máximo de los datos que esta unidad va a utilizar.

- El Host lee toda la información de configuración de la unidad USB. Este proceso lleva algunos milisegundos para que se complete.

- Basado en la información de configuración y en cómo la unidad USB puede ser usada, el Host asigna un valor de configuración a la unidad USB. La unidad USB pasa al estado de configuración y puede señalar la cantidad de energía que utilizará. Desde el punto de vista de la unidad USB, está lista para usarse.

Cuando una unidad USB es removida, el hub envía una notificación al Host. Al recibir la información, el Host actualiza la información topológica.

## 2.2.4.5 Descriptores USB

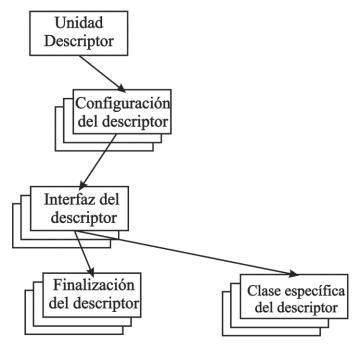

Los descriptores son utilizados por las Unidades USB para informar al Host de sus requerimientos. Un descriptor es una estructura de datos con un formato definido. Cada descriptor comienza con un campo de un byte para identificar el tipo de descriptor. Cada unidad USB debe tener por lo menos los descriptores que se muestran en la Figura 2.12 para que pueda ser reconocida por el servidor [3, 5, 22].

**Unidad Descriptor**: El dispositivo USB sólo puede tener un descriptor. Este descriptor muestra información sobre la versión del dispositivo USB, el tamaño máximo de los paquetes,

el identificador del fabricante, el identificador del producto, la versión del producto o el número de las posibles configuraciones que el dispositivo puede tener.

Figura 2.12 Descriptor USB [3].

Configuración del descriptor: El dispositivo USB puede tener más de una configuración, aunque la mayoría de los dispositivos usan sólo una. Este descriptor especifica la forma en que será alimentado (alimentación a través del bus o alimentación externa), el máximo voltaje que soporta, las interfaces que pertenecen al dispositivo, el tamaño total de todos los descriptores de datos, etc. Por ejemplo, un dispositivo puede tener dos configuraciones, una para cuando es alimentado a través del bus y la otra cuando es alimentado por una fuente externa.

**Interfaz del descriptor**: Un dispositivo puede tener más de una interfaz. La principal información dada por este descriptor es el número de criterios de valoración utilizados por esta interfaz, la clase y la subclase USB.

**Finalización del descriptor**: Este descriptor incluye los parámetros de la dirección de entrada/salida (IN/OUT), el tipo de transferencia soportada (control, interrupción, bulk e isócrona) y el intervalo de los datos en caso de una transferencia por interrupción.

La arquitectura USB comprende cuatro tipos básicos de transferencia de datos [22, 24]:

• *Control*: Usada para configurar un dispositivo en el momento de conectarlo y puede ser usada por dispositivos de propósito específico.

- *Interrupción*: Se utiliza para cuando se trabaja en tiempo real y se requiere seguridad en la transmisión.

- *Bulk*: Se usa cuando se manejan grandes cantidades de datos por lo que requiere de un ancho de banda suficiente.

- *Isócrona*: Ocupa una cantidad del ancho de banda USB configurando la latencia de entrada de los datos. También llamada transferencia de flujo continuo en tiempo real.

### 2.3 Entorno de desarrollo LabVIEW

LabVIEW es un entorno de programación gráfica usado por ingenieros e investigadores para desarrollar sistemas sofisticados de medición, pruebas y control. Esta plataforma de desarrollo fue creada por National Instruments y actualmente funciona sobre sistemas operativos como MAC, UNIX, Windows y GNU/Linux [13].

Los programas en LabVIEW no se escriben en forma textual, en lugar de ello se utilizan íconos gráficos y cables en una especie de diagrama de flujo. El entorno de desarrollo cuenta con una gran cantidad de bloques prediseñados con funciones específicas que proporcionan al usuario facilidad en el desarrollo de programas. Los programas en LabVIEW son llamados instrumentos virtuales (VIs, *Virtual Instruments*), porque con su apariencia y funcionamiento imitan a los instrumentos reales. Cada VI consta de dos partes diferentes [14]:

- El *Panel Frontal* es la interfaz con el usuario, permite interactuar con el usuario cuando el programa se está ejecutando. Los usuarios podrán observar los datos del programa actualizados en tiempo real. En esta interfaz se definen las entradas por medio de botones, campos de texto, listas numéricas, selectores booleanos, etc. También se definen las salidas con indicadores booleanos, textuales, numéricos o gráficos.

- En la interfaz del *Diagrama de Bloques* se colocan e interconectan los íconos para realizar una determinada función.

Gracias a su entorno gráfico, LabVIEW facilita la programación para desarrollar sistemas que requieren la comunicación de la PC con hardware a través de módulos con

puertos RS-232, USB y Ethernet. Ofrece una integración de diversos dispositivos de hardware y brinda bibliotecas integradas para un análisis avanzado y visualización de datos [13].

LabVIEW cuenta con métodos para la comunicación de software desarrollado en otros lenguajes, estos métodos implican una de las siguientes acciones [26]:

- Utilizar protocolos específicos de la plataforma.

- Usar llamadas a funciones de los siguientes tipos de bibliotecas compartidas:

- Bibliotecas de enlace dinámicos (DLL) en Windows.

- Fragmentos de códigos en Macintosh.

- Bibliotecas compartidas en UNIX.

- Crear un código de interfaz de nodo (CIN, Code Interfaz Node) para llamar a código escrito específicamente para vincular VIs.

Las llamadas de funciones de biblioteca de LabVIEW y del CIN se realizan mediante objetos gráficos escritos en lenguaje convencional de LabVIEW. Aparecen en el diagrama a bloques como iconos con terminales de entrada y salida. La vinculación de código externo a LabView incluye los siguientes pasos [13]:

- Compilar el código fuente y vincular al código ejecutable. Si ya se cuenta con un archivo DLL compilado, este paso no es necesario.

- LabVIEW llama al código ejecutable cuando el nodo se ejecuta.

- LabVIEW pasa los datos de entrada desde el diagrama de bloques al código ejecutable.

- LabVIEW retorna los datos del código ejecutable al diagrama a bloques.

## 2.3.1 Llamadas a las funciones de una biblioteca

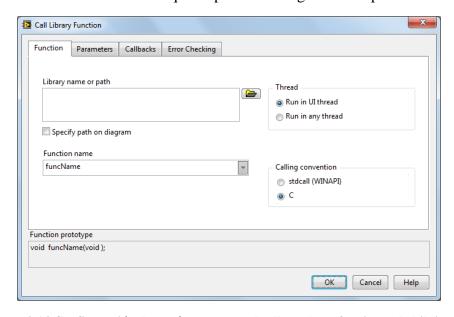

Las llamadas a las funciones de una biblioteca son más apropiadas cuando se tiene el código al que se desea llamar, o si se tiene conocimiento del proceso de creación de normas de bibliotecas compartidas. Debido a que una biblioteca utiliza un formato estándar entre varios entornos de desarrollo, se puede usar casi cualquier entorno de desarrollo para crear una biblioteca que LabVIEW pueda llamar. En la Figura 2.13 se muestra el módulo de LabVIEW que permite llamar a las funciones de una biblioteca [26].

Figura 2.13 Módulo para llamadas a funciones de una biblioteca.

En la configuración de este módulo se debe especificar la ruta de la DLL, la función a la que se quiera tener acceso, así como los parámetros de entrada y valor de retorno de ésta. En la Figura 2.14 se muestra la ventana en la que se pueden configurar estos parámetros.

Figura 2.14 Configuración de parámetros para las llamadas a funciones de biblioteca.

### 2.3.2 Detalles de un CIN

El CIN es un método general para ejecutar código C a partir de LabVIEW. En algunos casos se tiene mejor rendimiento usando CINs, porque la estructura de datos del la CIN está en el mismo formato que se almacena en LabVIEW [26].

## 2.3.3 Biblioteca de Enlace Dinámico para un HID de Atmel

Para que un dispositivo USB sea reconocido por una computadora se requiere de una biblioteca de enlace dinámico (DLL, *Dynamic Link Library*). Una DLL es un archivo ejecutable que permite a los programas compartir código y otros recursos necesarios para realizar determinadas tareas. Microsoft Windows proporciona DLLs con funciones y recursos para que los programas basados en Windows funcionen adecuadamente [9].

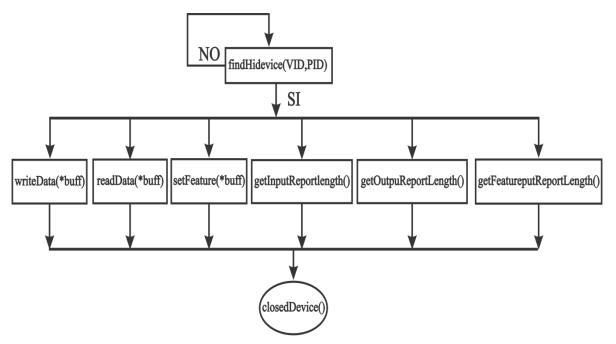

Las aplicaciones de Dispositivos de Interfaz Humana (HID, *Human Interface Device*) usan diferentes tipos de reportes (in/out) para enviar y recibir datos. La longitud de cada reporte es asignada en el Firmware y automáticamente detectada por la DLL después de las configuraciones del Firmware. En la Figura 2.15 se muestra un diagrama de la DLL proporcionada por Atmel, la cual permite comunicarse sólo con un dispositivo HID a la vez. Varios dispositivos no pueden ser manejados al mismo tiempo usando la misma DLL [25, 4].

Figura 2.15 Funciones DLL [25].

El papel de cada una de las funciones es el siguiente [25]:

- La función findHidDevice permite buscar unidades genéricas HID, usando el identificador del fabricante VID y el identificador del producto PID, abre un manejador si la unidad es identificada.

- La función ClosedDevice termina la comunicación con todas las unidades y los manejadores.

- La función *writeData* envía datos a la unidad. La longitud máxima del reporte de datos es proporcionado por la función *getOutputReportLength*. Si la longitud del paquete de datos excede el tamaño especificado por el firmware, el usuario tiene que enviar los datos en varios paquetes. Por el contrario, cuando la longitud de un paquete es menor a la especificada, la función completa con ceros las localidades vacías.

- La función *readData* lee los paquetes de datos enviados por la unidad.

- La función setFeature permite al usuario enviar un comando para controlar la unidad.

- La función *getOutputReportLength* permite al usuario obtener la longitud de los paquetes de datos de salida (paquetes de datos enviados de la PC a la unidad).

- La función *getInputReportLength* permite al usuario obtener la longitud de los paquetes de datos de entrada (paquetes de datos enviados de la unidad a la PC).

- La función *getFeatureputReportLength* permite obtener la longitud del reporte de configuración (paquete de datos de control enviados de la PC a la unidad).

# Capítulo 3 Definición del sistema

En este capítulo se describe el diseño del hardware de la tarjeta de adquisición de datos con interfaz USB y del software que se encargará de inicializar y atender los recursos de Entradas/Salidas Digitales, Contador de Eventos, Entradas Analógicas, Salidas Analógicas, Salidas con PWM y manejo del protocolo I2C del microcontrolador AT90USB646. También se explica el diseño del software en la PC que permitirá monitorear y atender los recursos de la tarjeta de adquisición de datos e interactuar con el usuario.

# 3.1 Metodología de desarrollo

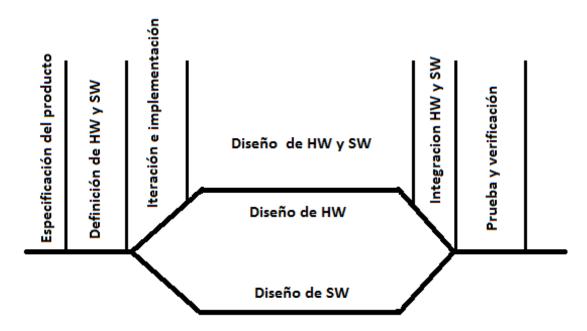

Para desarrollar un sistema de instrumentación electrónica es necesario realizar su planificación bajo alguna metodología. En el presente trabajo se utiliza la metodología de desarrollo para sistemas embebidos.

Un sistema embebido es un sistema que tiene un software embebido y hardware, lo que lo convierte en un sistema dedicado para una aplicación o parte específica de una aplicación o un producto [20].

En la Figura 3.1 se muestra un diagrama que contiene las diferentes etapas en el desarrollo de un sistema embebido [2].

En la etapa de *Especificación del producto* se define de forma clara y precisa la función del sistema, así como las entradas y salidas reales de éste y su interfaz con el

operador. Consiste en una descripción de los requerimientos técnicos y funcionales del sistema que se va a implementar para asegurar un producto robusto.

Figura 3.1 Diagrama de las fases para el diseño de un sistema embebido [2].

En la etapa de *Definición de HW y SW* se debe definir el hardware que se utilizará así como sus características principales. En la definición del software se especifican los requisitos, con base en la definición del hardware, en las especificaciones de ingeniería y en la definición general de requisitos del sistema.

En la etapa de *Iteración e implementación*, los componentes hardware y software son simulados o probados con la ayuda de herramientas especializadas, emuladores, para conocer con anticipación el comportamiento del sistema que se está implementando, pudiendo de esta forma anticipar y si fuera necesario corregir su funcionalidad.

En la etapa de *Diseño paralelo HW y SW* se diseñan detalladamente todos los componentes HW y SW especificados en los requerimientos, poniendo especial atención en mantener la coherencia entre los componentes en el producto final.

En la fase de *Integración de HW y SW* se deben integrar los componentes desarrollados para verificar que interaccionan correctamente entre sí.

En la etapa de *Prueba y verificación del producto* se realizan las pruebas del producto, si es preciso se realizan modificaciones y/o correcciones para adaptarlo a las necesidades del usuario.

## 3.2 Especificación del producto

El producto es una Tarjeta de Adquisición de Datos con interfaz USB y la interfaz gráfica de usuario para interactuar con la tarjeta. Las especificaciones iniciales del sistema son:

- Debe ser un sistema reconfigurable.

- Se comunicará a través del puerto USB.

- Debe contar con diversos recursos que permitan iniciar y terminar la comunicación.

- Se podrán inicializar los recursos que permitan el uso de Entradas/Salidas digitales,

Entradas/Salidas analógicas, puerto I2C, salidas en PWM y contador de eventos.

- Se debe configurar y monitorear los diversos recursos de la tarjeta a través de la interfaz de una computadora desarrollada bajo la plataforma de LabVIEW.

- Dicha interfaz debe de cumplir con los siguientes requisitos:

- Debe inicializar y finalizar la comunicación con la tarjeta.

- Debe proporcionar al usuario las herramientas para poder configurar los diversos recursos de la tarjeta.

- Contará con módulos que permitan al usuario conocer el estado de la conexión de la tarjeta.

- Contará con un espacio de trabajo para que el usuario pueda desarrollar aplicaciones, utilizando los módulos de la TAD.

- Debe presentar una interfaz amigable con el usuario final.

# 3.3 Definición de Hardware y Software

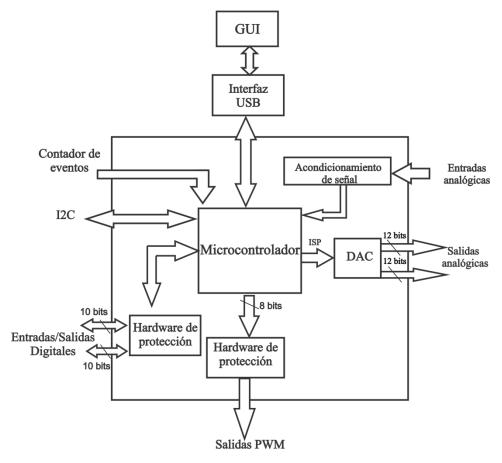

El diagrama a bloques mostrado en la Figura 3.2 describe las especificaciones del sistema. Este diagrama auxilia en la definición de los componentes de hardware y las especificaciones de los componentes de software que integran el sistema.

Figura 3.2 Diagrama a bloques de la especificación del sistema.

- Requerimientos de Hardware

- 16 pines digitales que podrán configurarse como entrada o salida.

- Puerto I<sup>2</sup>C.

- 2 Salidas analógicas de 12 bits.

- 2 contadores de eventos.

- 8 entradas analógicas de 10 bits referenciadas.

- 3 salidas PWM de 8 bits.

- Puerto de comunicación USB.

- Requerimientos de Software

- Módulos de configuración y atención de los recursos.

- Interfaz Gráfica de Usuario (GUI, *Graphical User Interface*).

### 3.3.1 Definición de Hardware

Según las especificaciones del producto, un microcontrolador es la parte principal de la tarjeta y se encargará de atender los diferentes recursos, ya que cuenta con los elementos necesarios para la adquisición y generación de señales analógicas y digitales.

#### 3.3.1.1 El Microcontrolador AT90USB646

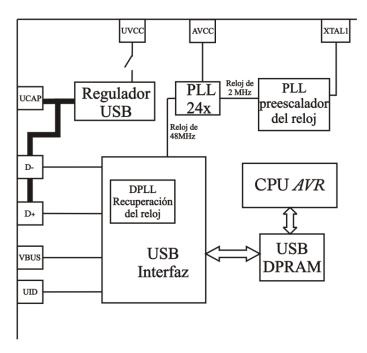

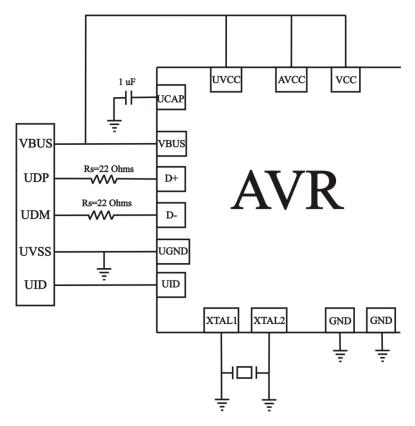

El microcontrolador AT90USB646 es un circuito integrado fabricado con tecnología CMOS (*Complementary metal-oxyde-semiconductor*) de bajo consumo, con núcleo AVR de 8 bits, arquitectura RISC y con un rendimiento cercano a 1 MIPS por MHz. A continuación se muestran algunos de los recursos con los que cuenta este microcontrolador [10].

- 64 KB de memoria de programa.

- 2 KB en EEPROM.

- 4 KB SRAM.

- 48 pines para I/O de propósito general.

- 32 registros de propósito general.

- 4 Temporizadores/Contadores con modos de comparación y generación de señales moduladas en ancho de pulso (PWM).

- Receptor / Transmisor Universal Sincrónico /Asincrónico (USART).

- Convertidor Analógico-Digital de 10 bits (*Analog Converter Digital*, ADC), con 8 canales.

- Perro guardián (*Watchdog Timer*) programable con oscilador interno.

- Puerto SPI.

- Controlador USB de alta velocidad (12 Mbps).

- Interfaz JTAG.

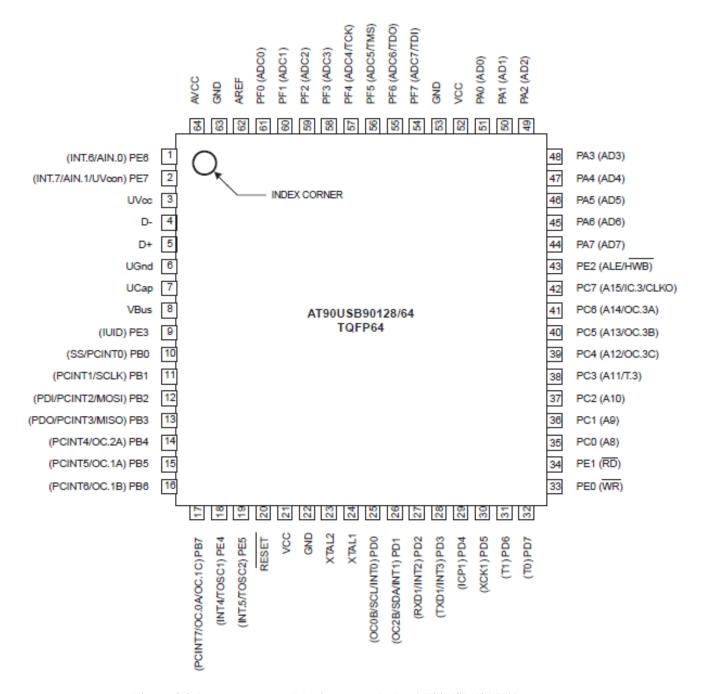

Comercialmente el microcontrolador AT90USB646 se encuentra en un encapsulado SMD de 64 pines. En la Figura 3.3 se muestra el aspecto externo del dispositivo, puede verse que cuenta con 6 puertos de 8 bits [10].

Figura 3.3 Aspecto externo del microcontrolador AT90USB646 [10].

En la Tabla 3.1 se muestra la distribución de los puertos del microcontrolador para cada recurso de la TAD.

Tabla 3.1 Asignación de los puertos del microcontrolador a los recursos de la TAD.

| Puerto en el<br>microcontrolador | Uso en la tarjeta                      |  |

|----------------------------------|----------------------------------------|--|

| Puerto A y E                     | Entrada/Salidas Digitales              |  |

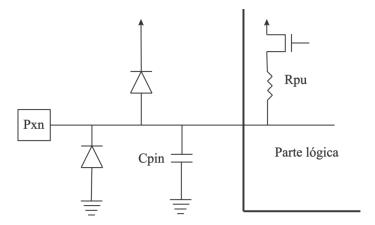

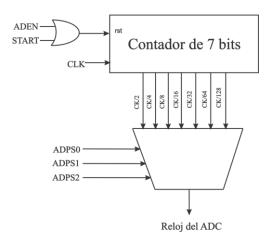

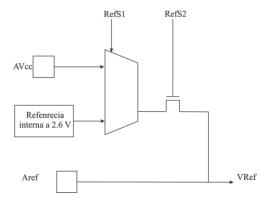

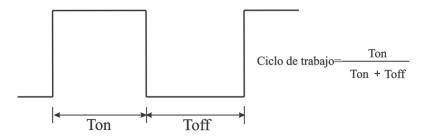

| Puerto B                         | Salidas analógicas                     |  |